Tool/software:

Hi, team

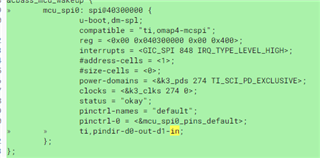

We want to use mcu_spi0 in r5 spl, we add mcu_spi0 in dts of r5 spl

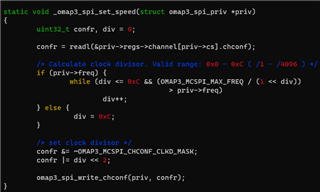

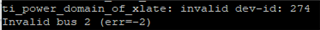

we use spi_get_bus_and_cs to get the spi, but error occurred

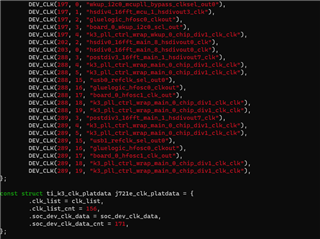

It seems like there is no 274 in soc_dev_list in arch/arm/mach-k3/j721e/dev-data.c,how can we add a new dev?

The default driver of pds(power-domains) is ti-power-domain.c, if we change it to ti-sci-power-domain.c, The board will get stuck during the r5 spl stage