Tool/software:

Hi, ti exports

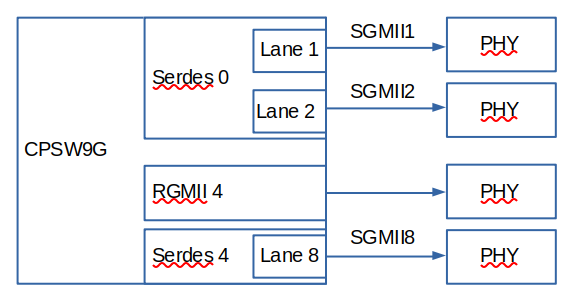

we are configured serdes0/4 as SGMII interface, and use cpsw9g in linux native driver mode, the Connection diagram as follows.

I modified DTS and RGMII4 is working now, but SGMII doesn't seem to be working,I have read many ticks on ti e2e,but still don't know how to solve the problem.

sdk version: ti-processor-sdk-linux-j7-evm-08_06_01_02

questions:

1、how to configuration SGMII in dts?

2、i saw some ticks mentioned that serdes0 is 2-Lane does not support single sgmii mode,so does we have a patch on sdk 8.6 about it(modify phy-cadence-sierra.c ?),and serdes4 also need to be modify?

3、we are used internal clock for serdes 0/4, does the clock configuration correct?

Can you help me check the DTS content,and tell me what modifications should be do can make SGMII1/2/8 work, thanks.

some content in k3-j721e-main.dtsi

cpsw0: ethernet@c000000 {

compatible = "ti,j721e-cpswxg-nuss";

#address-cells = <2>;

#size-cells = <2>;

reg = <0x00 0xc000000 0x00 0x200000>;

reg-names = "cpsw_nuss";

ranges = <0x00 0x00 0x00 0xc000000 0x00 0x200000>;

clocks = <&k3_clks 19 89>;

clock-names = "fck";

power-domains = <&k3_pds 19 TI_SCI_PD_EXCLUSIVE>;

dmas = <&main_udmap 0xca00>,

<&main_udmap 0xca01>,

<&main_udmap 0xca02>,

<&main_udmap 0xca03>,

<&main_udmap 0xca04>,

<&main_udmap 0xca05>,

<&main_udmap 0xca06>,

<&main_udmap 0xca07>,

<&main_udmap 0x4a00>;

dma-names = "tx0", "tx1", "tx2", "tx3",

"tx4", "tx5", "tx6", "tx7",

"rx";

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

cpsw0_port1: port@1 {

reg = <1>;

ti,mac-only;

label = "port1";

// status = "disabled";

};

cpsw0_port2: port@2 {

reg = <2>;

ti,mac-only;

label = "port2";

// status = "disabled";

};

cpsw0_port3: port@3 {

reg = <3>;

ti,mac-only;

label = "port3";

status = "disabled";

};

cpsw0_port4: port@4 {

reg = <4>;

ti,mac-only;

label = "port4";

status = "disabled";

};

cpsw0_port5: port@5 {

reg = <5>;

ti,mac-only;

label = "port5";

status = "disabled";

};

cpsw0_port6: port@6 {

reg = <6>;

ti,mac-only;

label = "port6";

status = "disabled";

};

cpsw0_port7: port@7 {

reg = <7>;

ti,mac-only;

label = "port7";

status = "disabled";

};

cpsw0_port8: port@8 {

reg = <8>;

ti,mac-only;

label = "port8";

status = "disabled";

};

};

cpsw9g_mdio: mdio@f00 {

compatible = "ti,cpsw-mdio","ti,davinci_mdio";

reg = <0x00 0xf00 0x00 0x100>;

#address-cells = <1>;

#size-cells = <0>;

clocks = <&k3_clks 19 89>;

clock-names = "fck";

bus_freq = <1000000>;

};

cpts@3d000 {

compatible = "ti,j721e-cpts";

reg = <0x00 0x3d000 0x00 0x400>;

clocks = <&k3_clks 19 16>;

clock-names = "cpts";

interrupts-extended = <&gic500 GIC_SPI 16 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "cpts";

ti,cpts-ext-ts-inputs = <4>;

ti,cpts-periodic-outputs = <2>;

};

};

serdes_wiz0: wiz@5000000 {

compatible = "ti,j721e-wiz-16g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 292 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 292 5>, <&k3_clks 292 11>, <&cmn_refclk>;

clock-names = "fck", "core_ref_clk", "ext_ref_clk";

assigned-clocks = <&k3_clks 292 11>, <&k3_clks 292 0>;

assigned-clock-parents = <&k3_clks 292 15>, <&k3_clks 292 4>;

num-lanes = <2>;

#reset-cells = <1>;

ranges = <0x5000000 0x0 0x5000000 0x10000>;

wiz0_pll0_refclk: pll0-refclk {

clocks = <&k3_clks 292 11>, <&cmn_refclk>;

#clock-cells = <0>;

assigned-clocks = <&wiz0_pll0_refclk>;

assigned-clock-parents = <&k3_clks 292 11>;

};

wiz0_pll1_refclk: pll1-refclk {

clocks = <&k3_clks 292 0>, <&cmn_refclk1>;

#clock-cells = <0>;

assigned-clocks = <&wiz0_pll1_refclk>;

assigned-clock-parents = <&k3_clks 292 0>;

};

wiz0_refclk_dig: refclk-dig {

clocks = <&k3_clks 292 11>, <&k3_clks 292 0>, <&cmn_refclk>, <&cmn_refclk1>;

#clock-cells = <0>;

assigned-clocks = <&wiz0_refclk_dig>;

assigned-clock-parents = <&k3_clks 292 11>;

};

wiz0_cmn_refclk_dig_div: cmn-refclk-dig-div {

clocks = <&wiz0_refclk_dig>;

#clock-cells = <0>;

};

wiz0_cmn_refclk1_dig_div: cmn-refclk1-dig-div {

clocks = <&wiz0_pll1_refclk>;

#clock-cells = <0>;

};

serdes0: serdes@5000000 {

compatible = "ti,sierra-phy-t0";

reg-names = "serdes";

reg = <0x5000000 0x10000>;

#address-cells = <1>;

#size-cells = <0>;

#clock-cells = <1>;

resets = <&serdes_wiz0 0>;

reset-names = "sierra_reset";

clocks = <&wiz0_cmn_refclk_dig_div>, <&wiz0_cmn_refclk1_dig_div>, <&wiz0_pll0_refclk>, <&wiz0_pll1_refclk>;

clock-names = "cmn_refclk_dig_div", "cmn_refclk1_dig_div", "pll0_refclk", "pll1_refclk";

};

};

serdes_wiz4: wiz@5050000 {

compatible = "ti,j721e-wiz-10g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 297 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 297 1>, <&k3_clks 297 9>, <&cmn_refclk>;

clock-names = "fck", "core_ref_clk", "ext_ref_clk";

assigned-clocks = <&k3_clks 297 9>;

assigned-clock-parents = <&k3_clks 297 10>;

assigned-clock-rates = <19200000>;

num-lanes = <4>;

#reset-cells = <1>;

ranges = <0x5050000 0x0 0x5050000 0x10000>,

<0xa030a00 0x0 0xa030a00 0x40>;

wiz4_pll0_refclk: pll0-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll0_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll0_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_pll1_refclk: pll1-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll1_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll1_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_refclk_dig: refclk-dig {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_refclk_dig";

#clock-cells = <0>;

assigned-clocks = <&wiz4_refclk_dig>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_cmn_refclk_dig_div: cmn-refclk-dig-div {

clocks = <&wiz4_refclk_dig>;

#clock-cells = <0>;

};

wiz4_cmn_refclk1_dig_div: cmn-refclk1-dig-div {

clocks = <&wiz4_pll1_refclk>;

#clock-cells = <0>;

};

serdes4: serdes@5050000 {

/*

* Note: we also map DPTX PHY registers as the Torrent

* needs to manage those.

*/

compatible = "ti,j721e-serdes-10g";

reg = <0x5050000 0x10000>,

<0xa030a00 0x40>; /* DPTX PHY */

reg-names = "torrent_phy", "dptx_phy";

resets = <&serdes_wiz4 0>;

reset-names = "torrent_reset";

clocks = <&wiz4_pll0_refclk>;

clock-names = "refclk";

#address-cells = <1>;

#size-cells = <0>;

// torrent_phy_dp: phy@0 {

// reg = <0>;

// resets = <&serdes_wiz4 1>;

// cdns,phy-type = <PHY_TYPE_DP>;

// cdns,num-lanes = <4>;

// cdns,max-bit-rate = <5400>;

// #phy-cells = <0>;

// };

};

};

some content in k3-j721e-common-proc-board.dts

&serdes_ln_ctrl {

idle-states = <J721E_SERDES0_LANE0_QSGMII_LANE1>, <J721E_SERDES0_LANE1_QSGMII_LANE2>, /* port1, port2 */

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_IP1_UNUSED>, <J721E_SERDES2_LANE1_USB3_1>,

<J721E_SERDES3_LANE0_IP1_UNUSED>, <J721E_SERDES3_LANE1_IP1_UNUSED>,

<J721E_SERDES4_LANE0_QSGMII_LANE5>, <J721E_SERDES4_LANE1_QSGMII_LANE6>,

<J721E_SERDES4_LANE2_QSGMII_LANE7>, <J721E_SERDES4_LANE3_QSGMII_LANE8>; /* port 8 */

};

&cpsw0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&cpsw0_mdio_pins_default &cpsw0_rgmii_pins_default &cpsw0_phy_reset_pins_default>;

};

&cpsw9g_mdio {

cpsw9g_phy1: ethernet-phy@1 {

compatible = "ethernet-phy-id002b.0980", "ethernet-phy-ieee802.3-c45";

reg = <0x1>;

reset-gpios = <&main_gpio0 96 GPIO_ACTIVE_LOW>;

reset-assert-us = <5000>;

};

cpsw9g_phy5: ethernet-phy@5 {

compatible = "ethernet-phy-id002b.0980", "ethernet-phy-ieee802.3-c45";

reg = <0x5>;

reset-gpios = <&main_gpio0 94 GPIO_ACTIVE_LOW>;

reset-assert-us = <5000>;

};

cpsw9g_phy6: ethernet-phy@6 {

compatible = "ethernet-phy-id002b.0980", "ethernet-phy-ieee802.3-c45";

reg = <0x6>;

reset-gpios = <&main_gpio0 55 GPIO_ACTIVE_LOW>;

reset-assert-us = <5000>;

};

cpsw9g_phy7: ethernet-phy@7 {

compatible = "ethernet-phy-id002b.0980", "ethernet-phy-ieee802.3-c45";

reg = <0x7>;

reset-gpios = <&main_gpio0 56 GPIO_ACTIVE_LOW>;

reset-assert-us = <5000>;

};

};

&cpsw0_port1 {

phy-handle = <&cpsw9g_phy1>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

// phys = <&cpsw0_phy_gmii_sel 1>;

phys = <&cpsw0_phy_gmii_sel 1>, <&serdes0_sgmii_link>;

phy-names = "portmode";

// phy-names = "portmode", "serdes-phy";

// phy-names = "mac", "serdes";

};

&cpsw0_port2 {

phy-handle = <&cpsw9g_phy5>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

// phys = <&cpsw0_phy_gmii_sel 2>;

phys = <&cpsw0_phy_gmii_sel 2>, <&serdes0_sgmii_link>;

phy-names = "portmode";

// phy-names = "portmode", "serdes-phy";

// phy-names = "mac", "serdes";

};

&cpsw0_port4 {

phy-handle = <&cpsw9g_phy7>;

phy-mode = "rgmii-id";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 4>;

// phy-names = "portmode";

// phy-names = "mac";

};

&cpsw0_port8 {

phy-handle = <&cpsw9g_phy6>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 8>, <&serdes4_sgmii_link>;

// phy-names = "portmode", "serdes-phy";

// phy-names = "mac", "serdes";

};

&serdes0 {

status = "okay";

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>;

serdes0_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz0 1>, <&serdes_wiz0 2>;

};

};

&serdes4 {

status = "okay";

assigned-clocks = <&serdes4 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz4_pll0_refclk>;

serdes4_sgmii_link: phy@3 {

reg = <3>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz4 4>;

};

};

ifconfig content:

root@j7-evm:~# ifconfig

docker0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

inet 172.17.0.1 netmask 255.255.0.0 broadcast 172.17.255.255

ether 02:42:d8:c0:a6:ac txqueuelen 0 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth0: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500 metric 1

inet6 fe80::3608:e1ff:fe58:fb10 prefixlen 64 scopeid 0x20<link>

ether 34:08:e1:58:fb:10 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 166 bytes 48364 (47.2 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth1: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500 metric 1

inet 192.168.2.21 netmask 255.255.255.0 broadcast 192.168.2.255

inet6 fe80::3068:69ff:feff:93f4 prefixlen 64 scopeid 0x20<link>

ether 32:68:69:ff:93:f4 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 2964 bytes 167688 (163.7 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth2: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

inet 192.168.2.22 netmask 255.255.255.0 broadcast 192.168.2.255

ether fe:bb:cd:89:e5:54 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536 metric 1

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 5652 bytes 507520 (495.6 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 5652 bytes 507520 (495.6 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

ethtool eth1

root@j7-evm:~# ethtool eth1

Settings for eth1:

Supported ports: [ ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Full

1000baseKX/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Full

1000baseKX/Full

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 1000Mb/s

Duplex: Full

Auto-negotiation: off

Port: Twisted Pair

PHYAD: 1

Transceiver: external

MDI-X: Unknown

Supports Wake-on: d

Wake-on: d

Current message level: 0x000020f7 (8439)

drv probe link ifdown ifup rx_err tx_err hw

Link detected: yes

SQI: 15/15