Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi team,

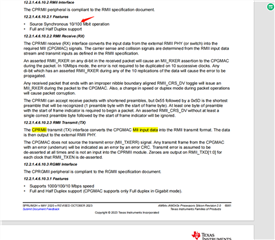

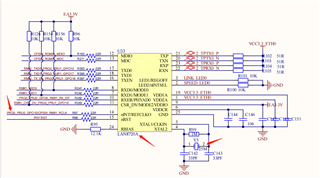

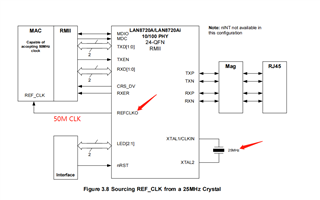

I encountered a problem while developing the RMII interface: I am unable to operate RMII in 100M mode.

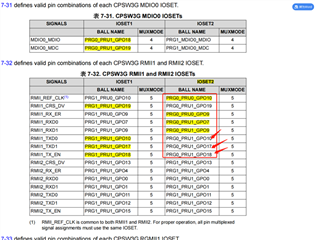

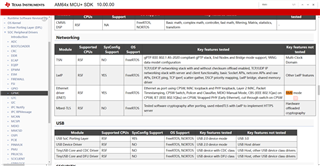

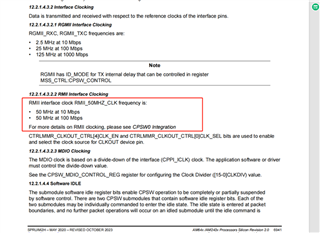

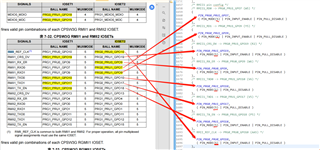

1) The search cannot find the RMII_EN, only GMII-IN and XGMII-EN (AM6442 only supports RMII RGMII), which are not within the interface support range of AM6442 CPSW.

How to ensure that RMII works at 100M?

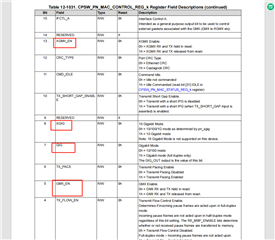

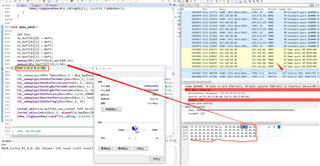

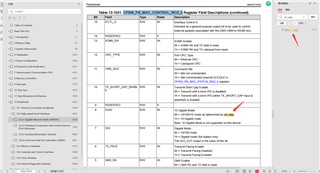

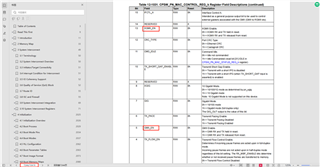

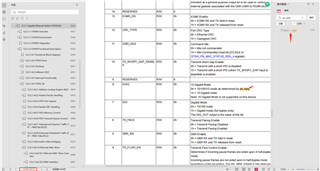

2) CPSW-PN_MAC-CONC-REG_k Register bit [8] XGIG indicates that the MAC transmission speed depends on pn-xig; TRM cannot retrieve the relevant instructions for pn_xig? How to make RMII work in 100 mode? (Currently, the 10M is working normally, but the setting method for the 100M cannot be found)

3)

I guess it's because the chip doesn't support RMII 100Mbps mode. I urgently hope that you can provide a simple example project of full duplex 100M rate in RMII interface mode to refute my point of view.

And regarding the description of the CTL_EN, I have searched the entire TRM and could not find the corresponding CTL_EN for the register. I have encountered similar issues multiple times during the development of AM6442, so I no longer have high trust in the TRM. This is also one of the reasons why I suspect the chip does not support RMII 100Mbps speed.

I really hope that your staff can refute my viewpoint with facts; Instead of repeatedly asking me to provide logs, the development of the RMII interface for this CPSW module has been frustrating for me (there is very little information, and last time I asked questions, they always simply asked me to provide logs. I really hope you can write your own test demo, I think you will also encounter the same dilemma as me).

Thanks & Best regards,

Jiahui