Other Parts Discussed in Thread: TPS6594-Q1, TPS65224, AM62A7-Q1, TPS6593-Q1, TPS22918

Tool/software:

HI Board designers,

I am designing my board using TPS6593 PMIC

Are there some common recommendation or observations that i should be aware?

Tool/software:

HI Board designers,

I am designing my board using TPS6593 PMIC

Are there some common recommendation or observations that i should be aware?

HI Board designers,

Refer below, FAQs, common queries and replies

If you are using the SK-AM62A-LP EVM with the TPS65931211-Q1 PMIC, then you can modify the hardware to change the default voltage on VDD_CORE which is supplied by the PMIC multi-phase Buck1/2/3.

The GPIO6 of the PMIC was configured to set the voltage on Buck1/2/3 with the following polarity:

During power up, the PFSM for the '1211 reads the state of GPIO6 10ms after it has enabled the 3.3V load switch. If GPIO6 is pulled up to that signal, BUCK123 will be 0.85V.

Therefore, from the PMIC perspective Pull GPIO6 HIGH to the 3.3V load switch signal

This information along with all the PMIC NVM configuration was documented in the following user's guide: https://www.ti.com/lit/pdf/slvucm3

Regards,

Sreenivasa

HI Board designers,

Refer below, FAQ

[FAQ] TPS6594-Q1: Residual Voltage Check

Regards,

Sreenivasa

HI Board designers,

Using TPS65224 for AM62A

Refer below, FAQ

Additional inputs

We get request from schematic review team to add a buffer between PMIC TPS65224 RSTOUT pin and SOC MCU_PORZ pin.

I think the reason is that the SOC MCU_PORZ will require the rising edge and falling edge. So would you like to share the detail.

Such as the rising edge slew rate, rising time and so on required by MCU_PORZ as input?

The PMIC nRSTOUT is a open drain slow ramp output from the PMIC.

When a slow ramp reset input is applies to the MCU_PORz there are likely chances that the internal reset circuit could glitch.

A discrete push pull output buffer is recommended to minimze the slew.

We do not have a spec for the MCU_PORz. The recommendation is faster the better. (<10ns)

if possible, could you help me confirm the timing relationship for Buck1 (VDD_CORE) and LDO0 (VDDR_CORE)

In the startup sequence the buck1 goes high at 5.9 ms and LDO3 (VDDR_CORE) at 6.45 ms. In the shutdown LDO3 goes down at 0.5 ms and buck 1 at 1 ms. Timings are measured from the enable rising/falling edge.

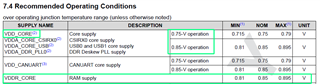

Partial IO - What about VDD_CANUART (core supply)?

For Partial IO, VDDSHV_CANUART (1.8V/3.3V) and VDD_CANUART (0.75V/0.85V) are both connected to always-ON rails. When Partial IO mode is not use, the CANUART supplies are connected to the same rails as the remaining IOs and CORE.

Regards,

Sreenivasa

Hi Board designers

Input regarding selection of PMIC:

The recommend PMIC(s) on the product folder or used on the SK or EVM schematics has been designed considering the power sequencing, supply rail output slew, nRSTOUT (reset output) delay output from PMIC connected to MCU_PORz after all the supplies ramp for clock to be stable and the sizing of the supply rails based on the processor worst case current draw.

When choosing an alternate non-TI PMIC, the recommendation for custom board designers is to review the relevant collaterals including the data sheet and Maximum Current Ratings document and follow the requirements/recommendations. The recommendation is to review the slew rate requirements, Power-up and power-down sequence sections of the data sheet and confirm the non-TI PMIC based power architecture follows the recommendation.

An important point to note is the processor does not support dynamic scaling of the core voltage or the analog supplies.

Inputs regarding supply decay

Refer below FAQ

I have placed the note in both sections because it applies to both power-up and power-down. The power-up sequence should not begin until all power rails are below 300mV, and the power-down sequence is not complete until all power rails are below 300mV.

Regards,

Sreenivasa

HI Board designers,

Inputs on power supply sizing:

Using Maximum Current Ratings application note vs Power Estimation Tool PET

The max current app note is representing the current draw for a group of rails. Please note that it is not expected for this current to necessarily be replicated in the power estimation tool. The PET will tend to show more average use case power while the max current app note is intended to be used for power supply sizing as it will allow for the max transient on these groups with some margin. The PET should not be used for power supply sizing.

Regards,

Sreenivasa

HI Board designers,

Note:

How were these pdn specs derived? Is it based on worst case analysis?

Yes it is based on worst case load transient estimates for a given SoC design.

The Target impedance for AM62x and AM62xSiP will be identical as the same worst case load transients exist on both designs since they share the same die.

Via sharing recommendations in the escape application note are only made to help guide a customer to escape the design with fewer vias in the VCA regions. The number of vias used for escaping signals will ultimately depend on the specific customer use-case, the number of interfaces that need to be implemented and the layer count. If the specific use case allows the customer to use more vias for VDD_CORE in the VCA regions, that is definitely a valid approach. Per-pin loop inductance guidelines are more applicable for single-pin supplies that are connected to a decap. In case of multi-pin supplies like VDD_CORE where there are a number of parallel connections to multiple pins/decap thru multiple vias, it is hard to tie it back in to a per-pin requirement. The most important target to meet is the impedance target specified in Table 7-6 of the PDN Applications note. This table is the same for AM62x and AM62x SiP.

We do not include Buck output inductance in PDN simulations.

For VDDS_DDR: we do not recommend using target impedance as the signoff for DDR.

Refer to the AM62x, AM62Lx DDR Board Design and Layout Guidelines which outlines all details of power aware SI/PI simulations

that need to be run. The eye mask checks from these power aware simulations are the signoff.

Power Distribution Networks: Implementation and Analysis

Sitara Processor Power Distribution Networks: Implementation and Analysis

https://www.ti.com/lit/pdf/sprac76

Note: The decoupling capacitor numbers and type on the SK/EVM are only intended to serve as a guideline for customers. The true pass/fail criteria is the target impedance published in the PDN app note.

High Speed Board design and Signal integrity simulation

https://www.ti.com/lit/pdf/spraar7

https://www.ti.com/lit/pdf/spracn9

https://www.ti.com/lit/pdf/sprabi1

Inputs on PDN

Please refer below inputs i received:

Please note these are only recommendations and they need to contact their EDA vendor on what works best for their specific simulation environment.

1、Do I need to separate VDD_CORE-1 to 17 for simulation, or use VDD_CORE as a Port?

TI>> You can lump all VDD_CORE BGAs together as a single terminal for the port

2、Do I need to include the PMIC FB loop in the simulation?

TI>> If you are simulating only for AC impedance (target impedance checks) this is not required. The board layout from the inductor onwards (inductor not included) can be modeled and PMIC FB loop can be studied separately.

3、 Is the simulation starting frequency from 1Hz or from a minimum of 100kHz for the capacitor S2P?

TI>> There should be some DC frequency points added. Please check with your EDA vendor on the exact setup and simulation points needed to generate causal models.

I added additional inputs related to PDN and decoupling capacitors for reference.

The voltage at the device ball must never be below the MIN voltage or above the MAX voltage for any amount of time. This requirement includes dynamic voltage events such as AC ripple, voltage transients, voltage dips, and so forth

PCB design & Dcap scheme combine to form your board's Power Distribution Network (PDN) that should meet recommended SoC PI performance targets for robust processor operations. Each PCB design has a "unique finger-print" based upon component placements, power & Gnd routing, layer assignments, via qtys & locations, Dcap mounting & loop inductance, Dcap parameters, etc. As a result, an optimized Dcap scheme will vary from one PCB design to another but should provide a system PDN that meets PI performance targets when combined together. Similarly, the PI simulation tools can impact the estimated ZvsF response values, especially above 3.0MHz where non-3D extraction tools can return better Z values (10-15% less than more accurate 3D tools). This ican be due to a non-3D tool is only extracting a PCB's X & Y design elements & assuming a power & Gnd via inductances. Due to the 3D nature of current flow across & through a PCB from power & Gnd planes on different PCB layers, a 3D extraction gives a more accurate series inductance estimate needed to more accurately model power & Gnd vias which leads to a more accurate power rail impedance (ZvsF) response

it would be difficult to comment on reducing the amount of decoupling caps without going through the exercise ourselves. That said, you can likely prioritize the high-current and sensitive analog rails, then look to share bypass caps when you hit space constraints. Having decap as close to the BGA as possible will reduce inductance and improve their efficacy (two supply vias with a shared decap would be better than a decap located far away in most circumstances).

Please be aware that each PCB design is unique and may need different Dcap scheme to meet recommended PI parameter targets

Regarding decoupling capacitors, the recommendation is to start with the EVMs decoupling and then optimize (if needed) based on your power simulation results.

For the placement of the Caps and values, we would still recommend using the EVM as a reference along with the PDN document.

SK uses an EMI Filter at 1uF, can I replace it with a general ceramic capacitor?

The SK performance has been tested with 3-T terminal caps.

You may have to add multiple 2-T caps for each cap and perform simulations to finalize the values.

AM62A7-Q1: Sitara Impedance Help

These are the target impedance estimates for AM62A rails. These can be taken as the target impedance requirements for the respective rails.

We do not have target impedance estimates for the other rails.

| Voltage Rail | Freq Range | Target Impedance (mOhms) |

| VDD_CORE (0.75V) | Low (< 1MHz) | 7.0 |

| Mid (1 - 20 MHz) | 11.7 | |

| High (20 - 50 MHz) | 23.4 | |

| VDD_CORE (0.85V) | Low (< 1MHz) | 6.9 |

| Mid (1 - 20 MHz) | 11.4 | |

| High (20 - 50 MHz) | 22.9 |

We have a high confidence in the target impedance estimates from a simulation standpoint, as our own boards have been designed to these requirements.

Does VDD_CORE (0.85V) rail refer to the same VDD_CORE pins as VDD_CORE (0.75V), but with target impedance if 0.85V is supplied to VDD_CORE?

OR, does VDD_CORE (0.85V) refer to the VDDR_CORE (0.85V) supply pins?

With regards to the VDD_CORE, the target impedance should refer to the same pins with either 0.75V and 0.85V supplied. The load transients and supply noise tolerances will be slightly different for the different voltages and so the target impedances will also differ slightly.

SPRAC76G does not list VDD_DDR Target Impedance across frequency ranges, it says "For more information, see AM62Ax DDR Board Design and Layout Guidelines." But this document also does not provide VDD_DDR Target Impedance across frequency ranges (as far as I can tell).

Please provide VDD_DDR Target Impedance across frequency.

We do not recommend using VDD_DDR Target impedance across frequency as an appropriate metric for signoff, due to very low load transients. For DDR signoff, we recommend running Power-aware Signal Integrity simulations as outlined in the AM62Ax DDR Board Design and Layout Guidelines App note.

Note:

We do not include Buck output inductance in PDN simulations.

For VDDS_DDR: we do not recommend using target impedance as the signoff for DDR.

Refer to the AM62Ax, AM62Px, AM62Dx LPDDR4 Board Design and Layout Guidelines which outlines all details of power aware SI/PI simulations

that need to be run. The eye mask checks from these power aware simulations are the signoff."

For frequencies above 50 MHz the board decoupling caps do not play a critical role. SoC and Package decaps (if any) will be dominant beyond 50 MHz

PDN application note

https://www.ti.com/lit/an/sprac76g/sprac76g.pdf

Regards,

Sreenivasa

HI Board designers,

E2E links for reference

All parts we sell are already pre-programmed. Under no circumstances will you ever receive a part with no programming on it.

The TPS6593-Q1, the TPS6593 is the generic portion of the part number.

TPS6593XXXXRWERQ1, the XXXX denotes a specific programming placed onto the device, as you see on the product page all devices have the TPS6593XXXXRWERQ1 naming scheme.

Are you not able to turn on your device, if so please open another E2E ticket so we can address your concerns there rather than here as this question is for acquiring PMICs not troubling shooting, thank you.

Regards,

Sreenivasa

Hi Board designers,

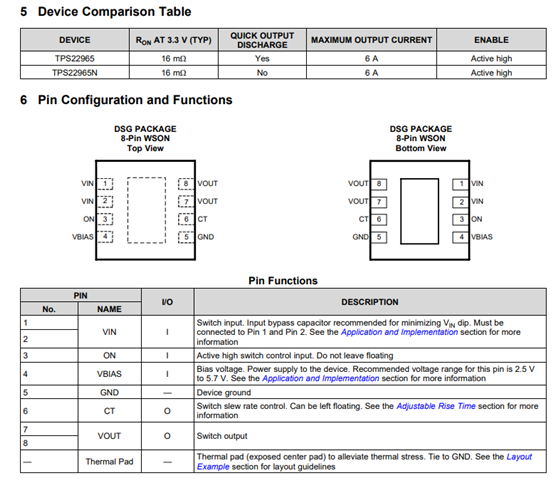

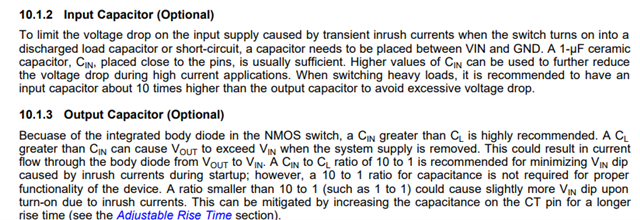

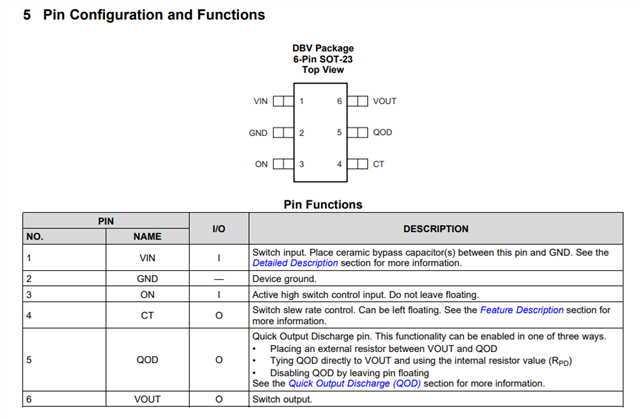

Refer below input related to eFuse caps and pinout

TPS22918 5.5-V, 2-A, 52-mΩ On-Resistance Load Switch

Regards,

Sreenivasa