Tool/software:

Hello engineers from TI:

We have a custom development version that uses the C6657 DSP chip and the boot mode we use is SRIO Boot.

Our hardware architecture adopts the design of FPGA+DSP. The FPGA writes the image into the DSP through SRIO and runs it on the DSP. We have successfully tested this technical route. And the DDR has been successfully tested through the manual provided by TI

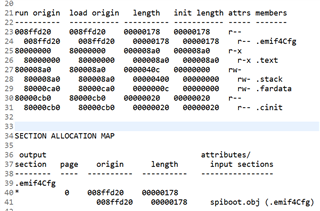

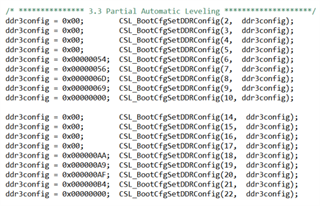

Now we want to place the. text segment on the DDR, so we need to initialize the DDR during the boot phase. By reading the SPRUG5C user manual, we found that TI provides a boot cinfiguration table in the boot table to initialize the DDR.

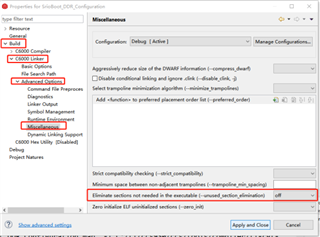

By referencing FAQ:https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1171336/faq-tms320c6657-how-to-run-the-direct-spi-boot-example-on-ti-c6657-evm-without-ibl

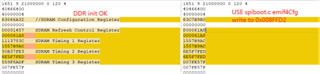

we created a project to port the code from spidoot. c into our testing project and wrote the content of emif4Cfg to 0x008ffd20 using SRIO. However, after testing, DDR was not successfully initialized.

Therefore, I have the following questions:

1. Can adding a DDR configuration table to the srio boot table initialize DDR during the SRIO boot and then write the. text segment to DDR.

2. If the technical solution for problem one is feasible, does it only need to write the content of emif4Cfg to 0x008ffd20 during the initialization process using the DDR configuration table in the srio boot? Do I need to write certain registers to trigger DDR initialization?