Other Parts Discussed in Thread: AM68

Tool/software:

Dear Team,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Dear Team,

Hi D.,

Reposting my email response:

"as for the PCIe PTM thread, unfortunately Jian is no longer an active employee at TI, so it will be hard to find the exact documentation that Jian is referring to in the 4 year old forum thread. Additionally, there is no PCIe PTM software implementation planned for the AM68 devices.

The most recent related activity that I could find is this FAQ for AM64 using RTOS: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1409291/faq-processor-sdk-am64x-how-to-enable-rtos-based-pcie-ptm/5396014#5396014. But as a warning, there are no RTOS based PCIe driver for the AM68 devices, and the RTOS code base used for AM68 and AM64 are slightly different, so the portability of this FAQ to AM68 is questionable. However, the PCIe controller IP on the SoC are the same, so the Linux driver is the same, so the example can be referenced somewhat (aka, what registers are important, and the flow)."

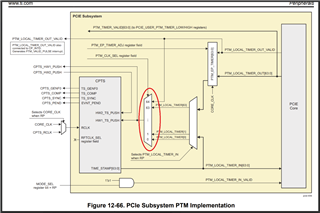

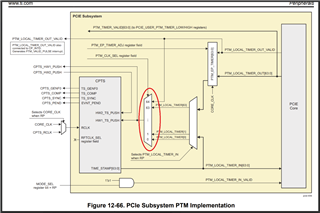

-> Also can you tell if the output from the red marked block can be connected to the HW2_TS_OUS or needs to be connected to HW1_TS_PUSH?

Looks to be only connected via HW1_TS_PUSH to CPTS inside PCIe subsystem and CPTS_HW1_PUSH is the signal going out of PCIe subsystem directly from that mux.

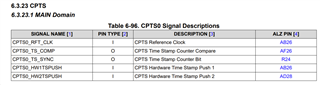

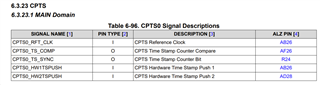

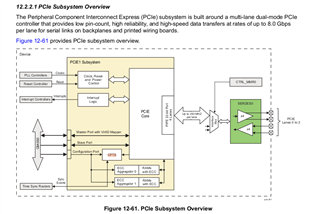

->Does the PCIE Subsystem use the Main Domain CPTS0 or does it have a dedicated PCIe CPTS?

There is a CPTS module inside the PCIe subsystem:

Regards,

Takuma

Hello D.,

as I was involved in that original thread maybe I can help you at least to some degree.

-> Is it possible that you share the TI programing model of PTM ( PCIe) and J7 implementation mentioned by Jian in the e2e thread ?

To be honest Jian never convinced me of the "TI method" for the AM65x. Basically this relied on the PCIe core driving the local PTM clock "between" each PTM cycle with a local clock. ONLY if the EP and the RC shared a common reference clock (not strictly necessary) and ONLY if the RC clocked its PTM master clock with this reference clock (not necessary, and in case of an x86 w/ SSC definitely not true) would this work. Luckily later designs like the AM64x provide more flexibility and that allowed us to implement proper time synchronization over PTM between an x86 RC and an AM64x EP. The AM68x should be similar to the AM64x in that regard.

I believe the "J7 implementation" referred to the ResponseD endianess issue. There was originally some ambiguity in the PCIe specification, and the AM65x SR 1.0 as well as Intel's Apollo Lake got it "wrong". The AM65x SR 2.0 had the endianess for ResponseD messages configurable, so it could adapt to either. Later designs like the AM64x (and I believe all the J7 variants) were fixed to use the "correct" endianess.

There are several restrictions both in the PCIe IP core and the SoC timesync design that caused problems for some use-cases and required workarounds, plus some things we never got to work (on the AM64x, and some of the issues persisted on the AM67x).

Maybe if you could explain in more detail what you're trying to achieve I could give you some hints.

Regards,

Dominic

Hi All,

we saw on youtube https://www.youtube.com/watch?v=lcbs9PRMjs0 that Pekka Varis presented PTM on AM64.

As i understand the current implementation is in bare metal, but it will be also implemented in RTOS and Linux, please can you confirm this?

1) Can you provide the current source code for PTM?

2) As we need this under Linux do you have a time frame when PTM will be available in Linux SDK?

3) How can we directly contact with Pekka regarding this matter?

Best Regards,

d.

Hi D.,

1) Can you provide the current source code for PTM?

1) You may reference this FAQ: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1409291/faq-processor-sdk-am64x-how-to-enable-rtos-based-pcie-ptm

2) As we need this under Linux do you have a time frame when PTM will be available in Linux SDK?

2) No plans, and no time frame.

3) How can we directly contact with Pekka regarding this matter?

3) Pekka mainly works with the low power processors (aka, AM62x~AM65x). He can help if this is one of the low power processors, but it will be hard to get their support for AM68x.

Regards,

Takuma

Hi Takuma,

Regarding 2) Questions was when they plan to have the PTM for AM64 in RTOS and Linux SDK.

Do they have timeframe for that ? then we can port it to AM68x

3) We are working on booth processors where AM64x is RC and AM68x EP ( but for internal reasons we first started with AM68x, thus the post )

How can we contact Pekka for the AM64x PTM?

Best Regards,

d.