Other Parts Discussed in Thread: SK-AM62

Tool/software:

In the schematic checklist of eMMC section:

7.2.2.1.1.3 Signals Termination

Provide the following:

• Connect a series resistor (0 Ω) for MMC0_CLK signal (close to processor) and external pulldown resistor for

MMC0_CLK signal (close to eMMC device).

• Connect external pullup resistor for the data line (MMC0_DAT0) (close to eMMC device). eMMC device (as

long as the eMMC device is compliant to the eMMC standard) has the pullups enabled for data signals

MMC0_DAT1..7 by default. The eMMC device will turn off its MMC0_DAT1..3 pulls when entering 4-bit mode

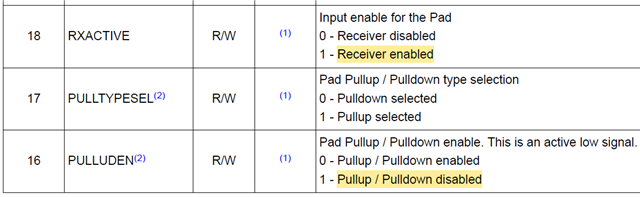

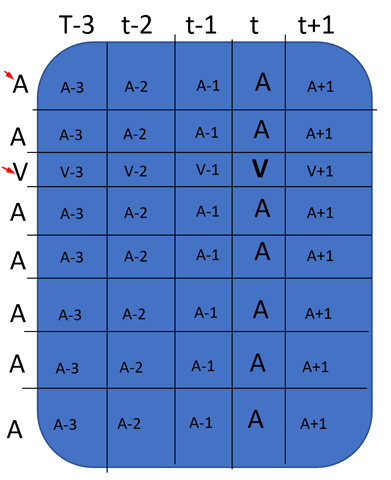

and MMC0_DAT1..7 pulls when entering 8-bit mode. The eMMC host software should turn on the respective

DAT pulls when it changes the mode.

#1. What is the purpose of 0ohm resistor for MMC0_CLK?

#2. Software turn on DAT pulls when changes the mode, is pulls must required on DAT pins? if so, why eMMC device turn it off from on during switch?

#3. Is it implemented in SDK to turn on DAT pulls when changes mode? did not find padconfig information in driver sdhci_am654.c