Part Number: AM623

Other Parts Discussed in Thread: SK-AM62B-P1

Tool/software:

Hi Experts,

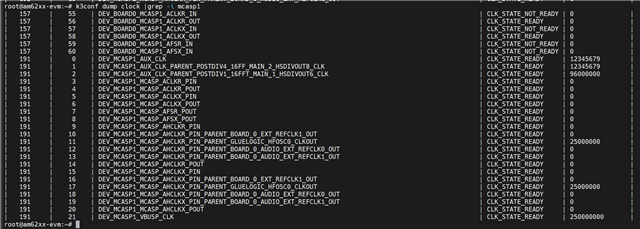

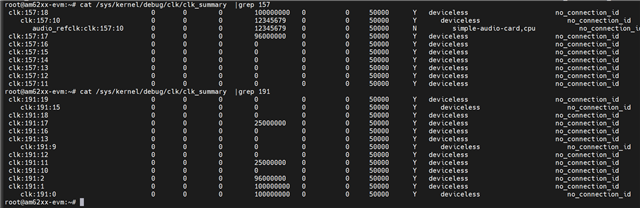

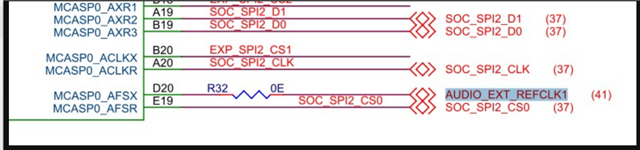

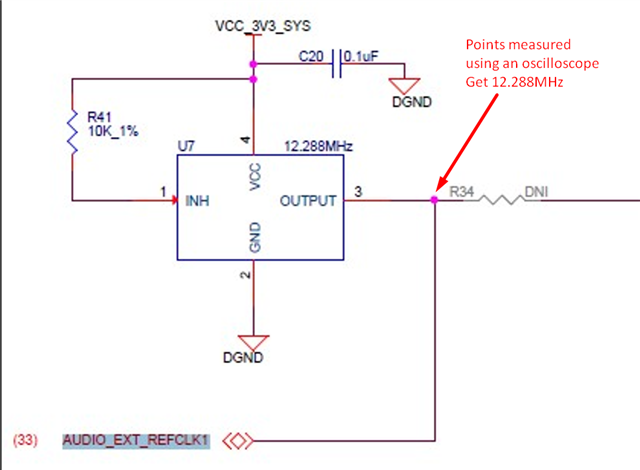

Test environment: SK-AM62B-P1 EVM & sdk-linux-am62xx-evm-11.00.09.04

Goal: Use McASP as independent 32 (TX/RX) sound channels (FS: 8K, CLK: 2M, 32 timeslot, 8 bits/timeslots mono), can play 32 sounds independently, record 32 channels independently, no Codec (not controlled by AM62x CPU)

Expected to achieve:

Use MCASP1 interface to generate fixed PCM signal

When executing aplay -D plughw:0,X test.wav (file format is also 8K/mono/ 16bits A/Mu law), you can see these signals (FS/CLK/...) appear in Codec TLV320.

Question 1: In the following method, I first use Dummy-Codec to replace TLV320, but I don't know if there is a more suitable sound card/codec settings to meet my actual needs?

Modifications for Dummy-Codec:

1. Download dummy-codec.c and modify .compatible = "linux,dummy-codec", recompile the Kernel

refer to the link: https://gitlabhost.argos-navy.ru/rockchip/rongpin/rk3588_android12/-/blob/master/kernel-5.10/sound/soc/codecs/dummy-codec.c

2. The DTS part is as follows:

A. Remove tlv320_mclk: clk-0, codec_audio: sound and &mcasp1 in k3-am62x-sk-common.dtsi

B. Add the following content to the root node of k3-am625-sk.dts

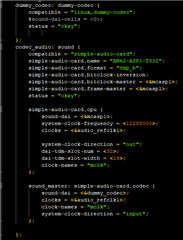

dummy_codec: dummy-codec {

compatible = "linux,dummy-codec";

#sound-dai-cells = <0>;

status = "okay";

};

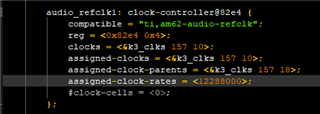

mcasp_mclk: mcasp-mclk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <2048000>; // 2.048MHz

};

codec_audio: sound {

compatible = "simple-audio-card";

simple-audio-card,name = "AM62x-Dummy";

simple-audio-card,format = "dsp_b";

//simple-audio-card,bitclock-inversion;

simple-audio-card,bitclock-master = <&mcasp1>;

simple-audio-card,frame-master = <&mcasp1>;

status = "okay";

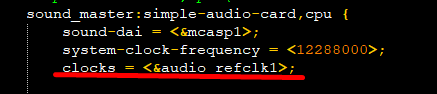

simple-audio-card,cpu {

sound-dai = <&mcasp1>;

};

sound_master: simple-audio-card,codec {

sound-dai = <&dummy_codec>;

clocks = <&mcasp_mclk>;

};

};

sound_master: simple-audio-card,codec {

sound-dai = <&dummy_codec>;

clocks = <&mcasp_mclk>;

};

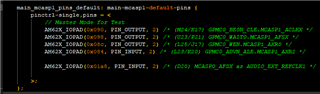

C. Add the following at the end of this file

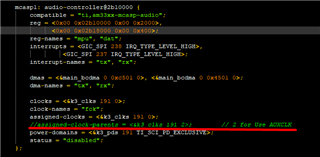

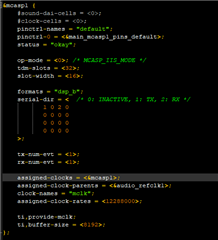

&mcasp1 {

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&main_mcasp1_pins_default>;

status = "okay";

op-mode = <0>; /* MCASP_IIS_MODE */

tdm-slots = <32>;

slot-width = <8>;

serial-dir = < /* 0: INACTIVE, 1: TX, 2: RX */

1 0 2 0

0 0 0 0

0 0 0 0

0 0 0 0

>;

tx-num-evt = <1>;

rx-num-evt = <1>;

ti,buffer-size = <8192>;

};

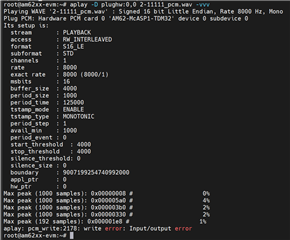

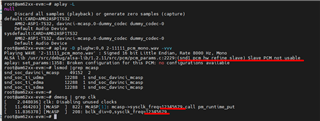

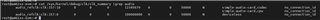

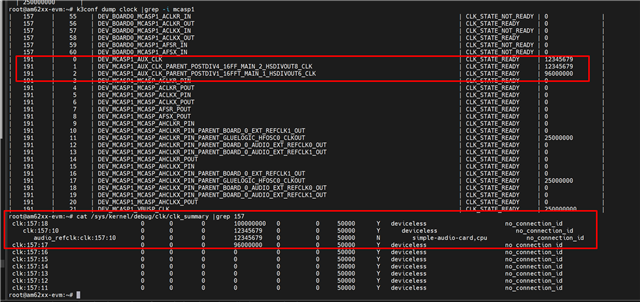

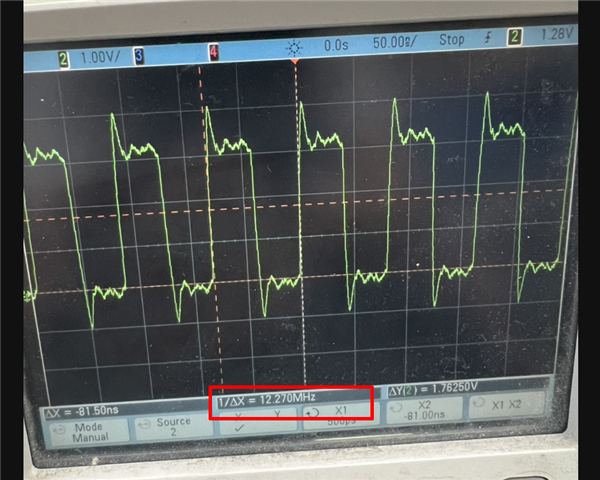

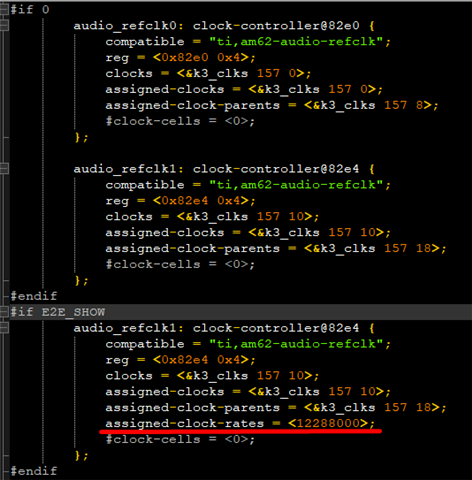

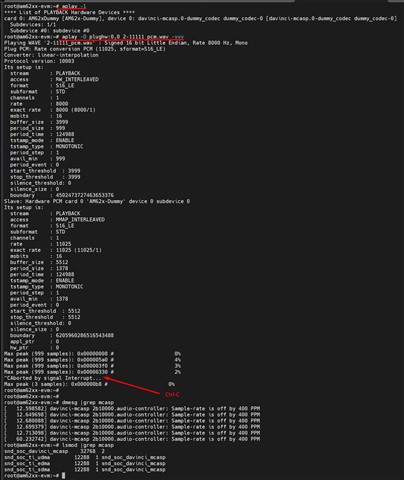

The test results are as follows:

Question 2: It seems that aplay cannot continue to execute, it stops somewhere, and there is no signal output on the oscilloscope. Which part is the problem?

Best Regards,

Brian