Part Number: AM623

Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

We are verifying AM6232 + 4Gb DDR4 in our new project and there are 2 issues found:

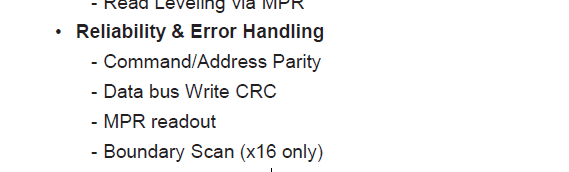

1. we tested UDQS and DQ12, the tDQS2DQ max is 1.0398 which is higher than the creteria 0.17UI, and tDQSCK is -350.37ps which is smaller than the creteria -225ps

2. we tested LDQS and DQ6, the tDQS2DQ max is 3UI whichi is also higher than the creterial.

Is there any registers to tweak the timing?