Other Parts Discussed in Thread: AM62P

Tool/software:

Hi:

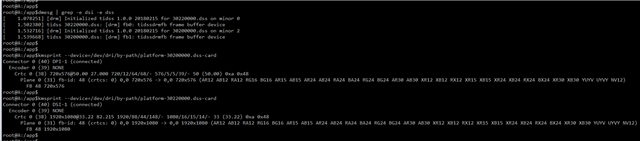

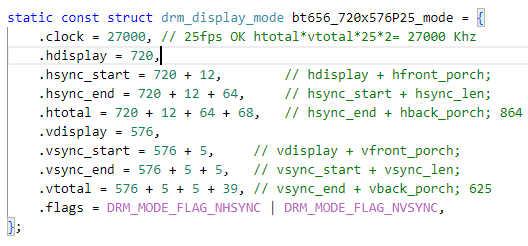

DPI BT656 Display Useing Progressive mode On Dothinkey is OK.

But Project need BT656 Interlaced mode , and do signal format conversion to CVBS, output CVBS Display on IVI.

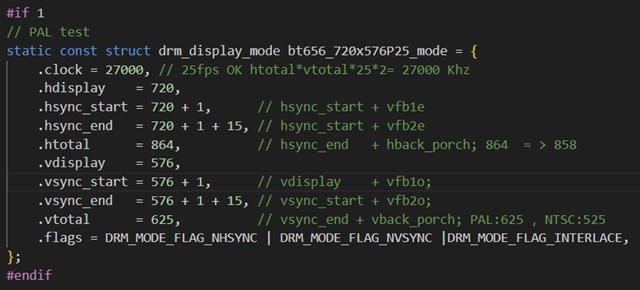

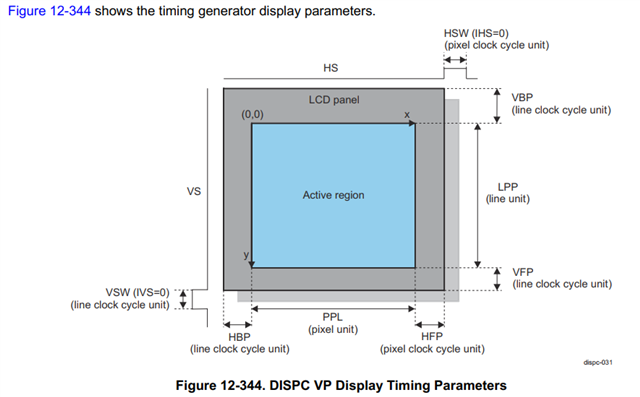

The pannel parame is :

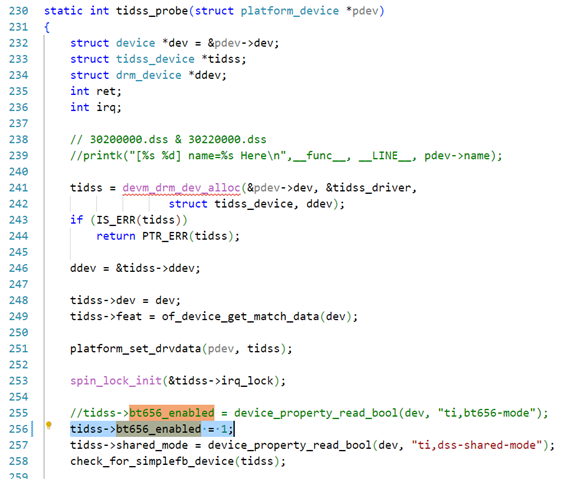

So How to Enable BT656 Interlaced mode, pls help!!!