Other Parts Discussed in Thread: TUSB8020B

Tool/software:

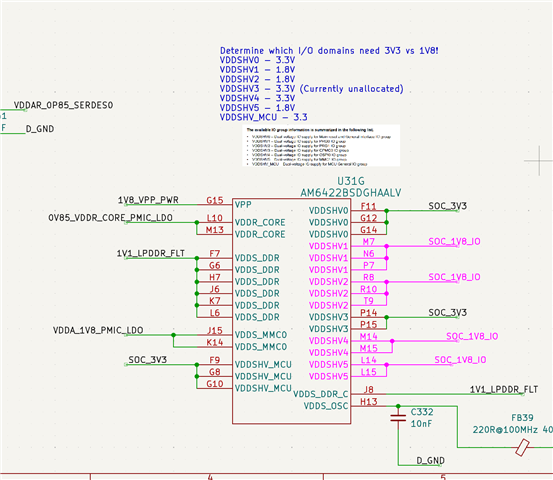

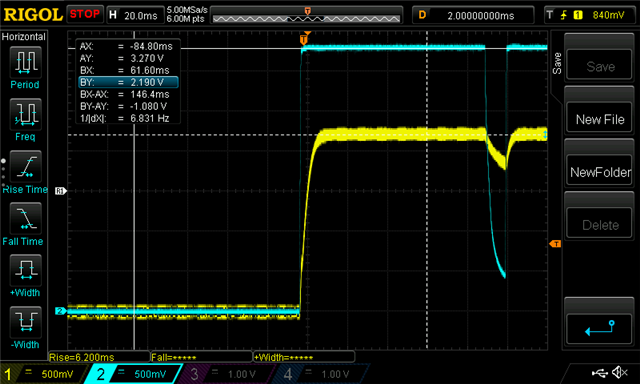

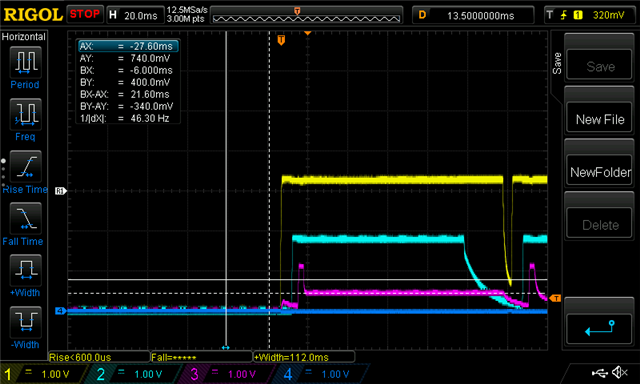

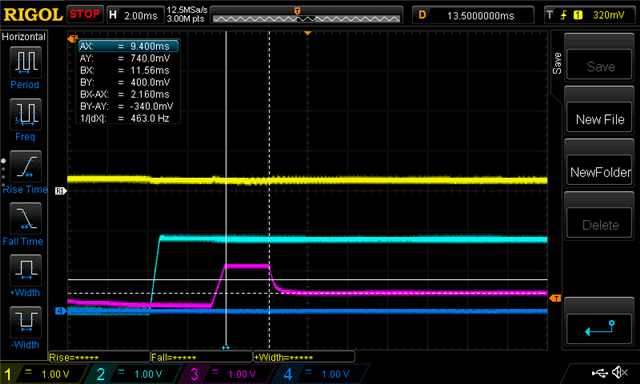

Hi all - I have a schematic review request for a design with a AM64X processor. Right now we're seeing the TPS6522053 unable to fully ramp up, and we're hoping that we can get some insights as to what might possibly be going on.

Thanks,

James