Hello,

Can the termination resistors be removed if following topology is used?

4 Memory chips:

2 chips for DDR0 (same PCB position, one chip on the TOP, one chip on the BOTTOM)

- one chip for DDR0 Data 0-15;

- second chip for DDR0 Data 16-31;

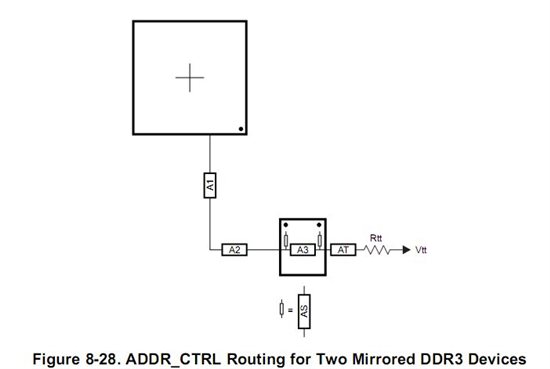

- DDR0 Control / Command / Clocks connected by T branch just under the memory chips

2 chips for DDR1 (same PCB position, one chip on the TOP, one chip on the BOTTOM)

- one chip for DDR1 Data 0-15;

- second chip for DDR1 Data 16-31;

- DDR1 Control / Command / Clocks connected by T branch just under the memory chips

This topology is supported by Freescale chips for DDR3 - Is it supported by C6A816x too?

Thank you,

- Robert