Hello,

I’m wondering if core Pll of C674x in my application is set appropriately, it is to its full power.

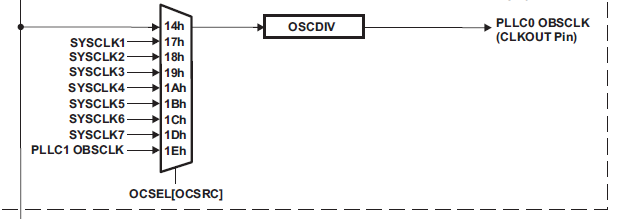

Is there a way to monitor the reached DSP core-Pll performance, a sort of DSP CLOCKOUT signal?

I know, it would be a 300 MHz signal which is rather demanding to measure.

Here’s my core-Pll setup that should lead to its speed of 300 MHz:

OSCIN=20 MHz (evaluated via OSCOUT)

PLLM = 15 (to reach: 300 MHz)

PREDIV=POSTDIV=0

I use CGT 6.1.23, and DSP/BIOS 5.42.01.09. CCS 5.5. The DSP is a C6747.

Many thanks!

Mladen