I am trying to get standby/resume working on our custom AM3354 based module. The board has two MT41K256M8DA-125 Micrel modules.

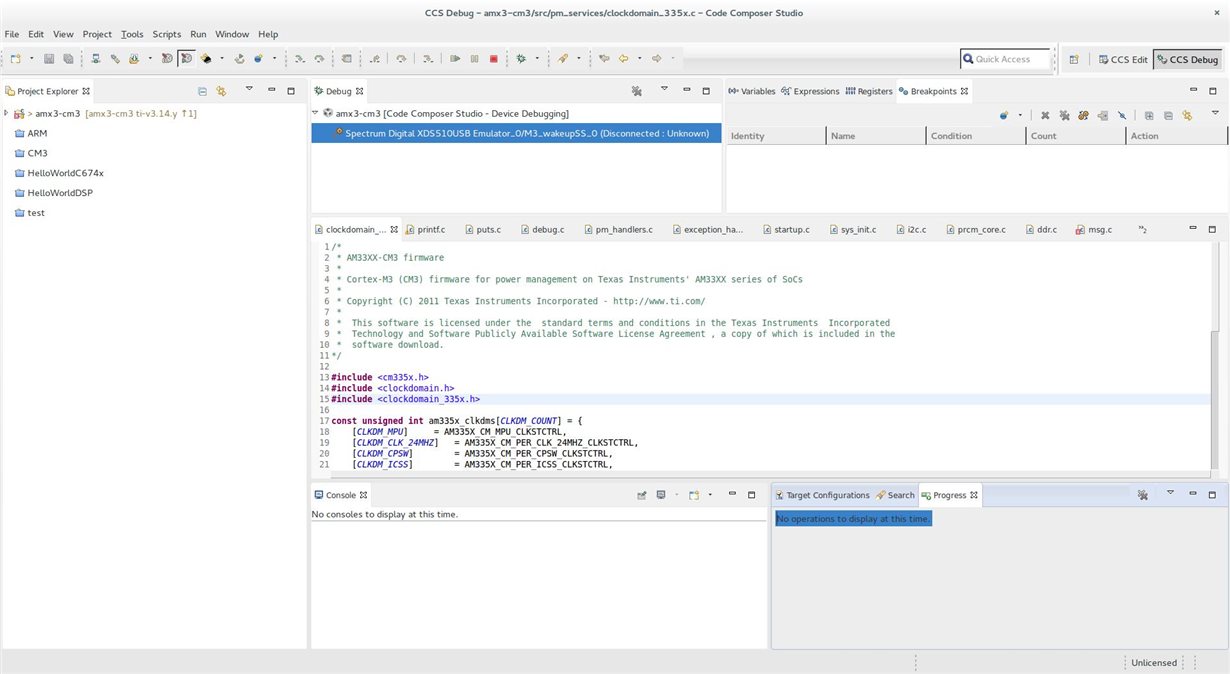

I have been able to reproduce the standby functionality using a BBB running the debian wheezy filesystem and the 3.14 ti kernel.

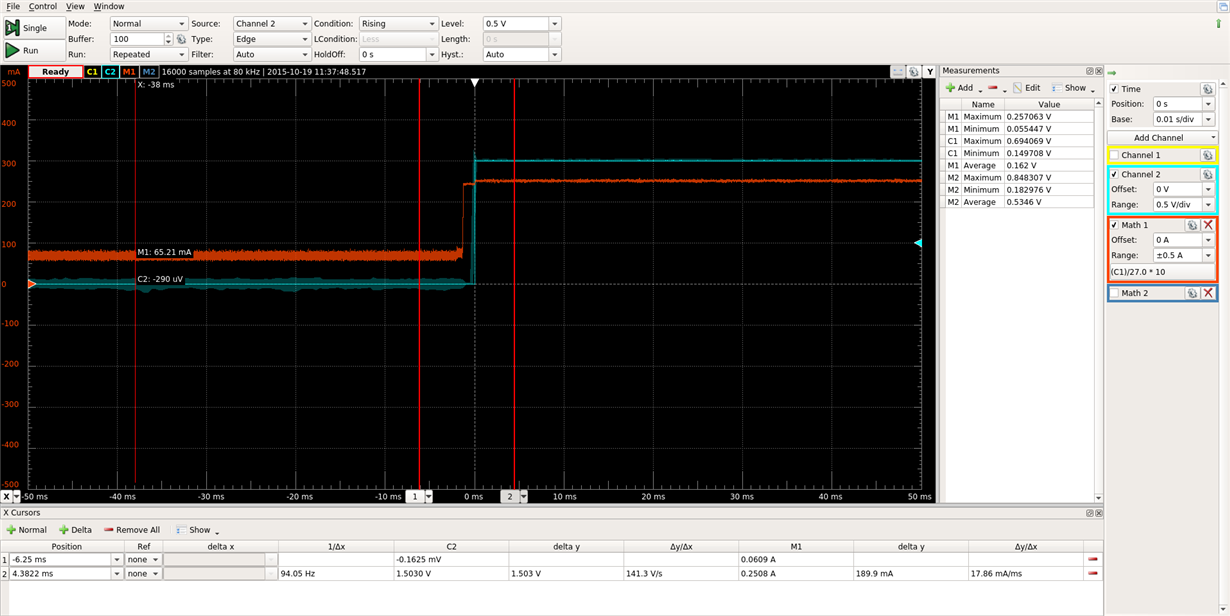

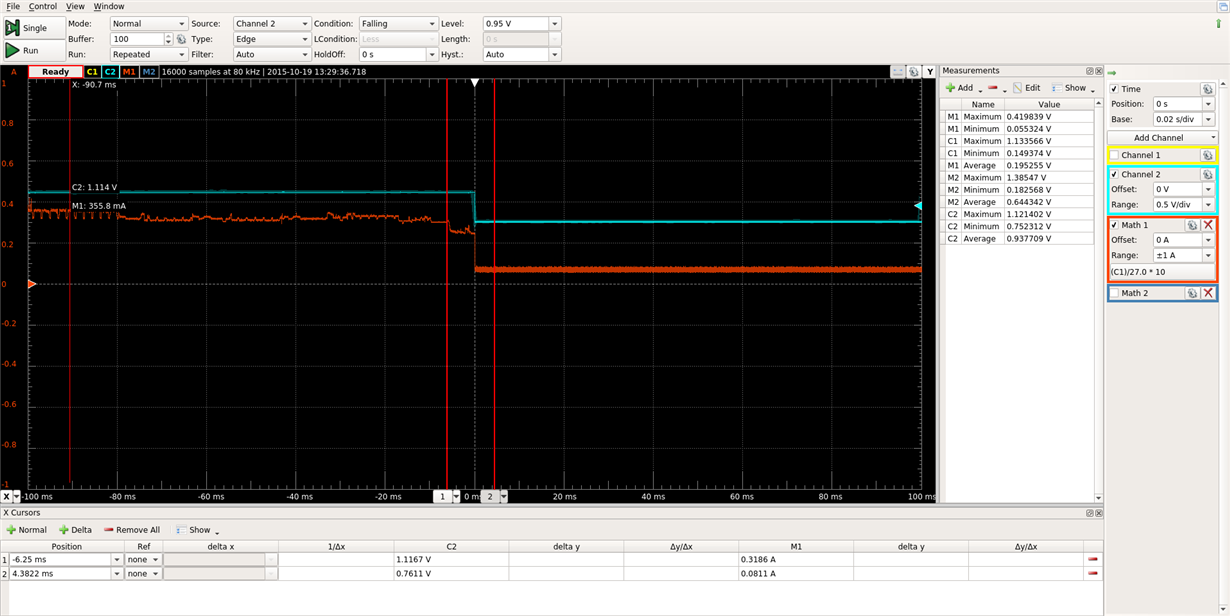

Booting the same kernel and filesystem on our board does not work. The system is able to go into standby but when the spacebar is pressed the system doesn't resume. I am able to see the power usage increase after trying to wake up the device and the reset button starts functioning.

My question is has anyone tested sleep mode when using 2 DDR3 modules? Is it possible that the 2 DDR3 setup could be the cause of this failure? What steps can I take to narrow down the cause of this problem.

Thanks

Jonathan Cormier