Hi everyone,

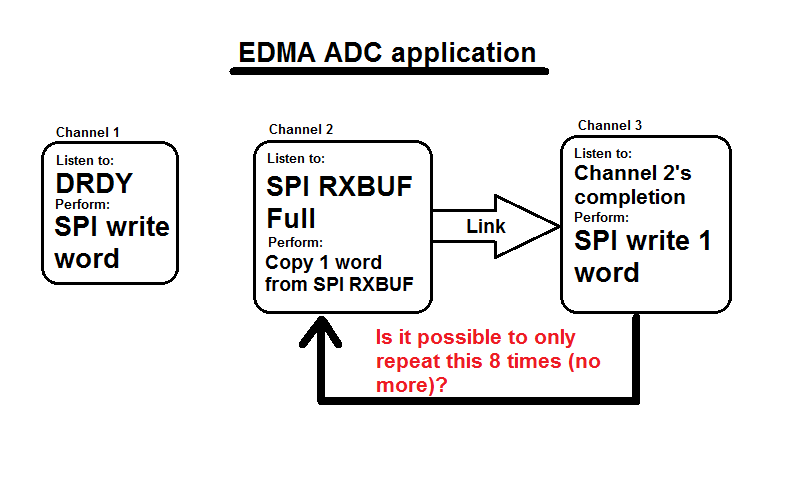

We have the following application: OMAP L132 reading ADC samples via SPI.

The ADC produces a single data ready (DRDY) interrupt and then the C6748 core starts to read 8x16bit words via SPI.

We are interested in changing this low level driver, which takes a lot of CPU time, to an EDMA application.

Is it possible to perform such transfer using EDMA? We couldn't find anythng suitable on the TRM.

Thank you in advance.

Yeho.