Hi Guys,

I'm trying to check driver support for nand in my custom DM385 board,

NAND Flash -> Spansion S34ML01G100TF100 -> 1Gib -> 128MiByte

I have followed

above document and added mtd & others in kernel as it said.

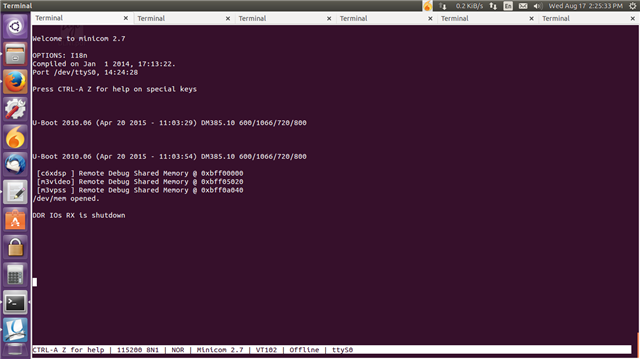

but still i'm getting

No NAND device found -> in dmesg

after checking driver support in kernel source code,

in drivers/mtd/nand/nand_ids.c

struct nand_manufacturers nand_manuf_ids[] = {

{NAND_MFR_TOSHIBA, "Toshiba"},

{NAND_MFR_SAMSUNG, "Samsung"},

{NAND_MFR_FUJITSU, "Fujitsu"},

{NAND_MFR_NATIONAL, "National"},

{NAND_MFR_RENESAS, "Renesas"},

{NAND_MFR_STMICRO, "ST Micro"},

{NAND_MFR_HYNIX, "Hynix"},

{NAND_MFR_MICRON, "Micron"},

{NAND_MFR_AMD, "AMD"},

{0x0, "Unknown"}

};

it doesn't have support for my spansion NAND Flash. where as compatibility wise it is every bit of samsung K9F1G08U0E.

So how do i add Spansion nand flash support in my kernel, so that it can detect manufacture id.

thanks & regards,

Ganesh