Part Number: TDA2EXEVM

Other Parts Discussed in Thread: TCAN4550

Hello,

The SPI chip select setup time(Time since CS goes low to SPI clock) is measured to be around 8.7 micro seconds.

But as per the TCAN4550 manual (tcss) value can be as minimum as 25ns.

Query 1: How this time can be minimized?

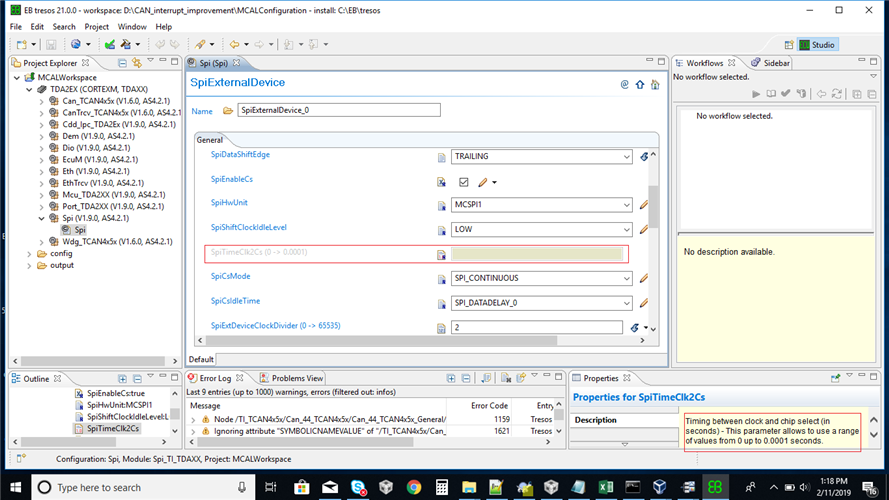

Query 2: Is this configurable using parameter SpiTimeClk2Cs? (As checked in Ebtresos tool for plugins as per delivery mcal_setupwin32_01.09.00.30, this cannot be configured, please find the attached snapshot of tresos window)

Thanks