Hi Team,

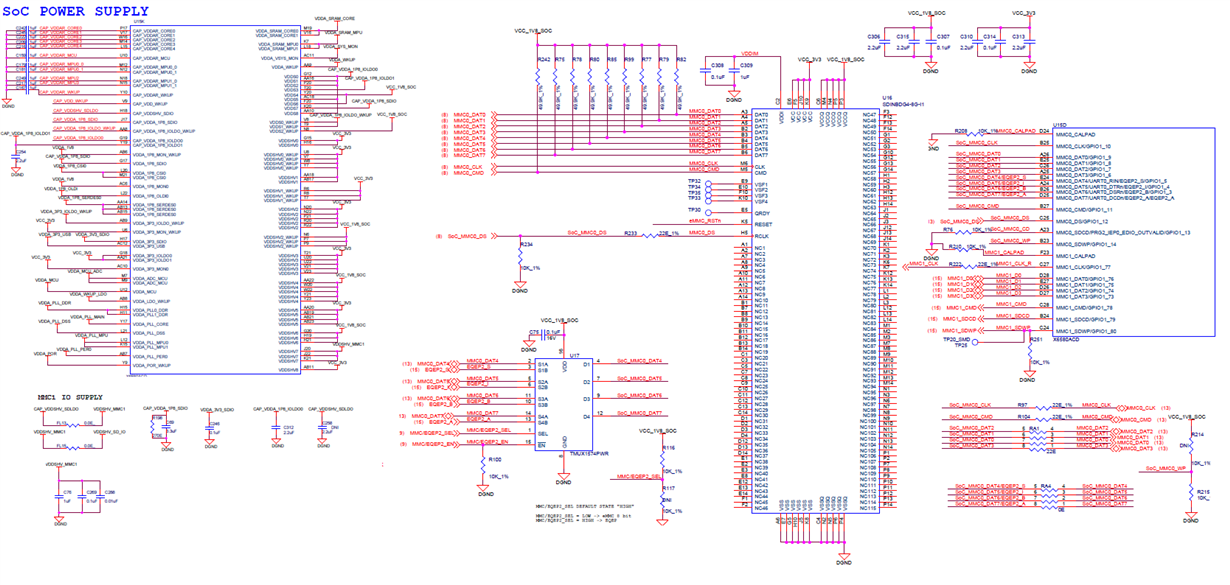

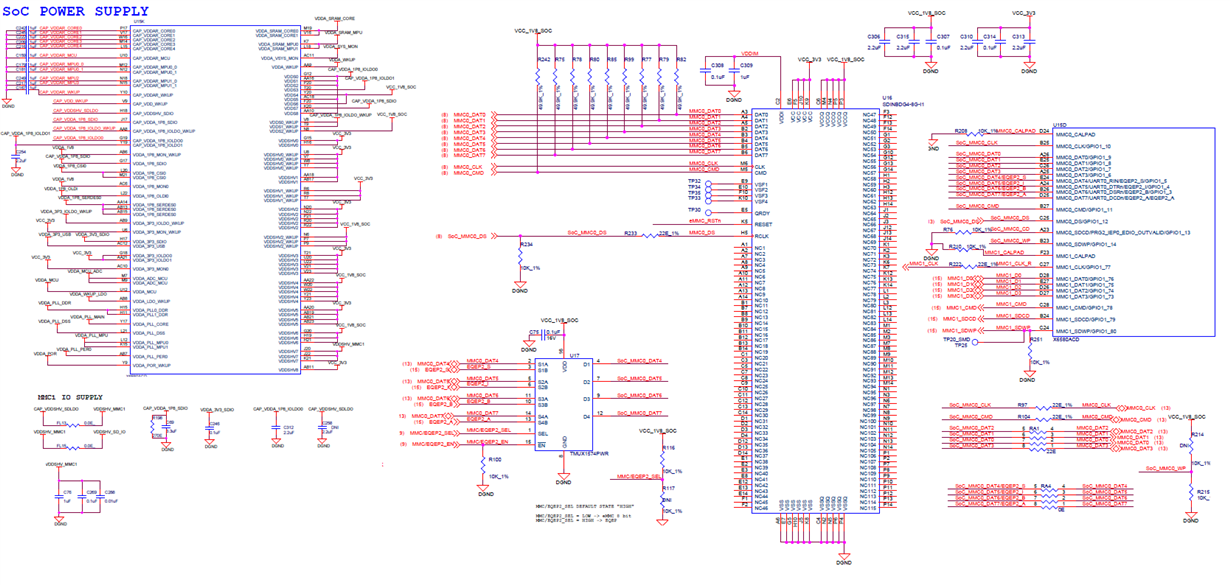

We have designed a board with AM5648 SoC. We are in board bring up stage and have observed a strange issue in few of our boards. Please find the details below:

1. We have set SD card as primary boot source and eMMC as secondary boot source.

2. We are operating eMMC in HS200 Mode. For initial few boards we have tested eMMC with RTOS test application, and have not observed any inconsistency.

3. However, for next set of boards among the same build, we observed inconsistency with eMMC test. Hence, we replaced the series resistor on clock path from 22E to 33E. After this we observed that it was working fine for few boards. But, few boards failed to boot after this re-work. As we have set MMC1 as primary boot device and MMC0 as secondary boot device, how can a rework on MMC0 is causing the board to fail during boot? Is there anything to do with the series resistor change. Please note that when we again replace the resistor to 22E, the board boots. However, eMMC test will fail.

4. Voltages and clock looks fine and the processor is out of reset all the time. Also note that when we downgrade the clock to 52MHz(SDR50), we are not observing any inconsistency issue with eMMC.

Appreciate your quick reply.

Regards,

Karthik