Other Parts Discussed in Thread: DS90C387A, , CDCVF2505

Our customer wants to connect AM5728 (VOUT2) to DS90C387A (Single-to-dual) with 144MHz PCLK, but it does not seem possible.

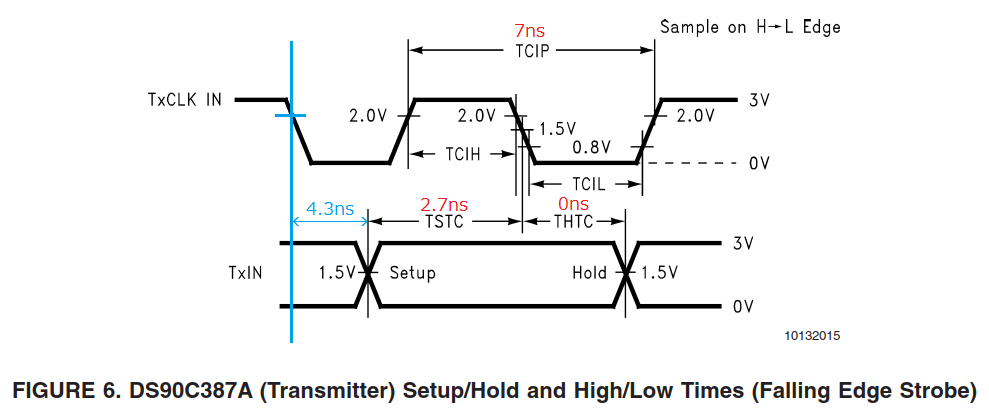

For DS90C387A, the setup time and hold time are as follows.

- TxIN Setup to TxCLK IN (TSTC): 2.7ns

- TxIN Hold to TxCLK IN (THTC): 0ns

For AM5728 (VOUT2), the delay time of each Manual IO Timings Modes that supports 144MHz PCLK is as follows.

- MANUAL1 (Alternate): 1.51ns (MIN) - 4.55ns (MAX)

- MANUAL3: 2.78ns (MIN) - 5.91ns (MAX)

- MANUAL4: 3.55ns (MIN) - 6.61ns (MAX)

To meet the setup time of DS90C387A, the maximum delay time must be less than 4.3ns, but AM5728 (VOUT2) does not meet it.

Can you tell me how to connect AM5728 (VOUT2) to DS90C387A with 144MHz PCLK?

Can AM5728 (VOUT2) be customized IO timings?

Best regards,

Daisuke