- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

Is it feasibility exist ?

if I used One DRAM.

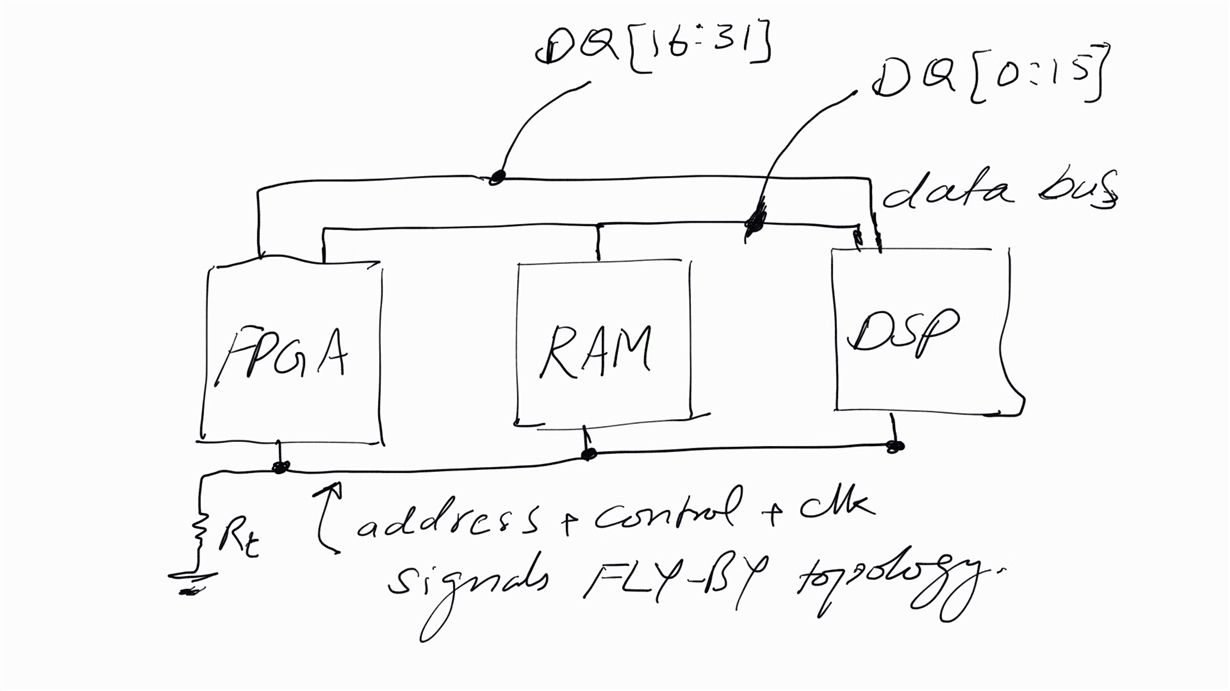

>First step > FPGA Write data from to DRAM through DDR interface. (16 bit).

> 2nd step > 66AK2G12 read data from same DRAM through DDR interface. (16 bit).

Hi again,

I would not say that's impossible as I just don't know that. What I know is that intended high speed link to FPGA is PCIe. With that one still can use DDR RAM as a pocket buffer between DSP and FPGA. On DSP side there is DMA, namely EDMA3 engine to perform data moves without CPU intervention. Particularly, it can be instructed to fetch data out of FPGA to desired location. Bear in mind, that would require FPGA design to be capable to handle multi-DWORD TLPs over PCIe, which may cost some efforts to your FPGA designer. Another possibility is to have DMA engine on FPGA side along with bus mastering capability. Then FPGA may push data to DSP's memory on its own. We used the latter approach for a while but dropped in favour of the former one.