hi all experts,

my EVM board is TIDEP-01002, now we have a projector, it support HDMI 1280x720 input.

and we run visionSDK 0304 on M4 core to control the DSS, and linux side graphy image by VDRM.

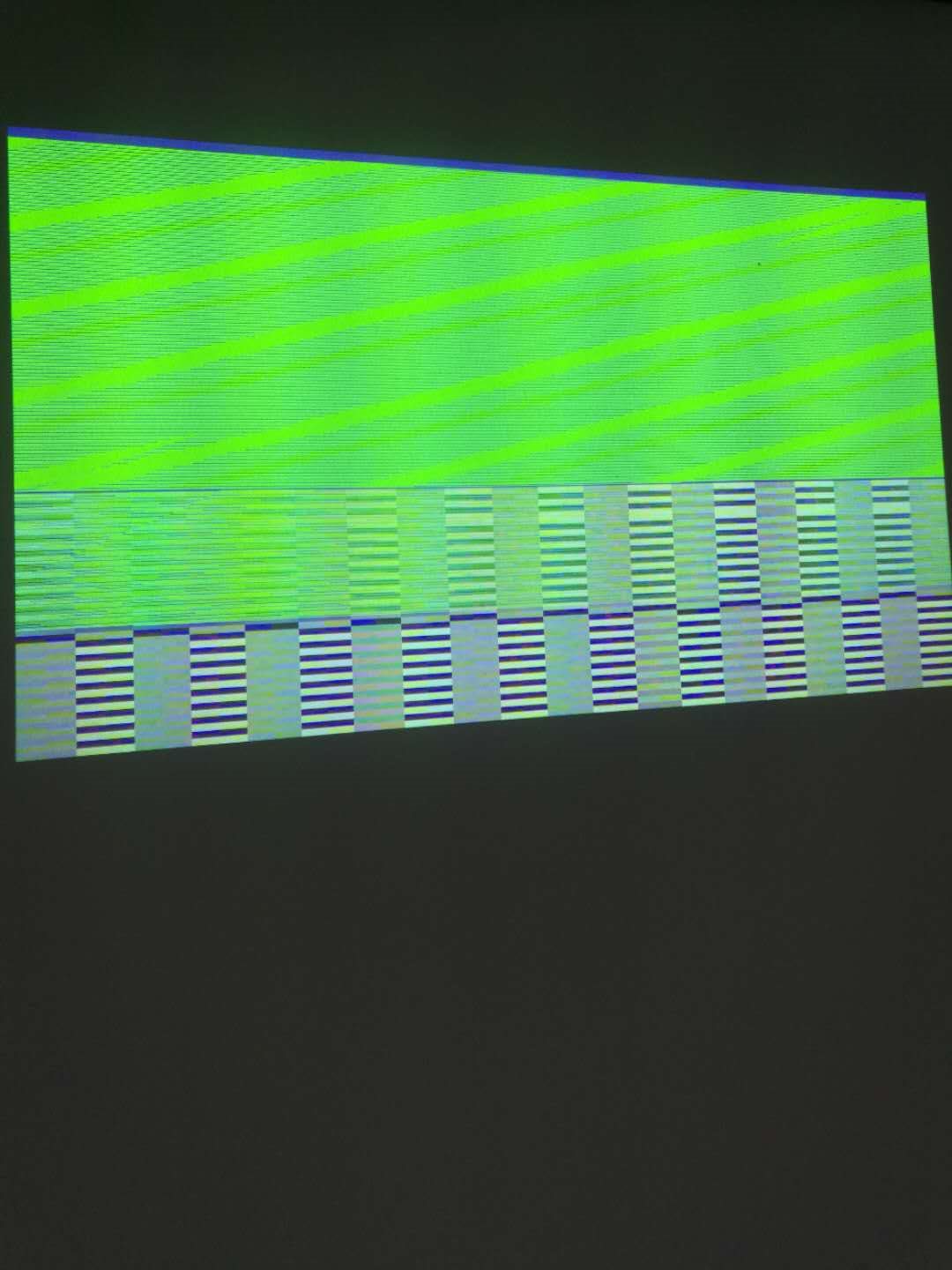

now we have the problem of projector can not show image correctly.

i create pipeline as following, use VID2 to display.

DispDistSrc_Infotainment-> Display_vid2

i set the VDRM in dts as following:

vdrm1: vdrm@1 {

/* For Android presentation mode window on 720p HDMI */

compatible = "ti,dra7-vdrm";

vdrm1_crtc0: crtc@0 {

compatible = "ti,dra7-vdrm-crtc";

x-res = <1280>;

y-res = <720>;

refresh = <50>;

supported-formats = <

DT_DRM_FORMAT_RGB565 DT_DRM_FORMAT_RGBX4444 DT_DRM_FORMAT_XRGB4444

DT_DRM_FORMAT_RGBA4444 DT_DRM_FORMAT_ARGB4444 DT_DRM_FORMAT_XRGB1555

DT_DRM_FORMAT_ARGB1555 DT_DRM_FORMAT_RGB888 DT_DRM_FORMAT_RGBX8888

DT_DRM_FORMAT_XRGB8888 DT_DRM_FORMAT_RGBA8888 DT_DRM_FORMAT_ARGB8888

DT_DRM_FORMAT_NV12 DT_DRM_FORMAT_YUYV DT_DRM_FORMAT_UYVY

>;

};

};

and i set the VID2 parameters as following:

pUcObj->Display_vid2Prm.rtParams.tarWidth = 1280;

pUcObj->Display_vid2Prm.rtParams.tarHeight = 720;

pUcObj->Display_vid2Prm.rtParams.posX = 0;

pUcObj->Display_vid2Prm.rtParams.posY = 0;

pUcObj->Display_vid2Prm.displayId = DISPLAY_LINK_INST_DSS_VID2;

i set the display parameters as following :

pVsObj->mDisplayPrms[1].displayType = CHAINS_DISPLAY_TYPE_HDMI_720P; //CHAINS_DISPLAY_TYPE_HDMI_1080P;

// Infotainment

pVsObj->mDisplayPrms[1].pipeID[0] = SYSTEM_DSS_DISPC_PIPE_VID2;

pVsObj->mDisplayPrms[1].zOrderPipeID[0] = SYSTEM_DSS_DISPC_ZORDER0;

{

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_HDMI;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_HDMI_OUTPUT;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

}