Hi Expert,

My customer wants to confirm regarding Jacinto6 I2C3 behavior and asks us to propose how to avoid issues with Jacinto6.

-----

1.Background

This questions is not a problem happened in Jacinto-6, but it happens with Competitor SoC.

Customer wants to know whether Jacinto-6 can avoid this problem when connecting Jacinto-6 with CP.

2.Bootup

A) External I2C slave device (called as “CP”), which is connected to Jacinto6 I2C3, makes both SCL and SDA pins to LOW level for about 2.5usec after booting up.

B) After that, CP does not output any signals and then CP waits for Master (=Jacinto6) signal.

C) CP is a slave device. But CP forces to LOW level only during booting up, then release SCL and SDA pins after about 2.5usec elapsed.

3 Questions:

[Q-1] Does CP device behavior cause Jacinto6 I2C3 error ? Please tell me any conditions in which Jacinto6 enters to the error.

Since Jacinto6 I2C3 is supporting multimaster, they wants to know if Jacinto6 illegally recognizes SCL=LOW & SDA=LOW as Start-Condition. And then, Jacinto-6 has stuck to wait for Device. Customer concerns about a possibility of those error.

If Jacinto6 has a register or something which can ignore entering into Start-Condition after setting by CP (SCL=LOW & SDA=LOW at boot-up and then those signals are released ), please tell us how to use the register.

[Q-2] Is there any ways to return from the error/stucks after entering into the illegal Start-Condition like [Q-1] ?

For example, after detecting time-out, resetting I2C3 is needed and then it brings to returning to Master mode etc.

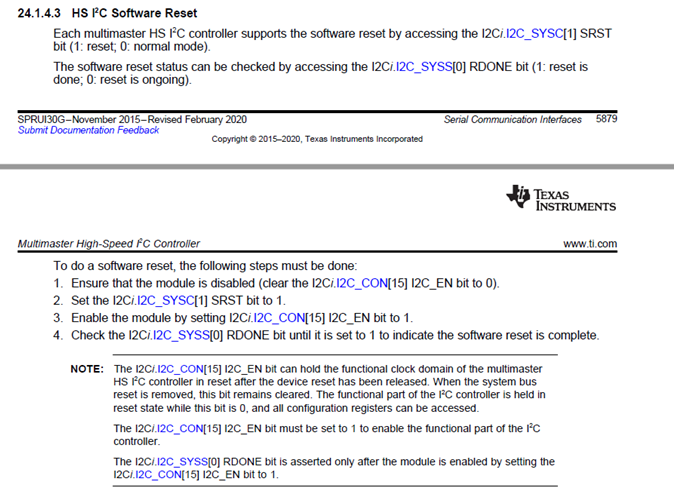

After I got this question from customer, I found "I2C Software reset" below in TRM. Is it effective to return from the illegal Start-Condition ?

[Q-3] If returning to the Master mode already implemented into SW, please tell us which SW should be referred to by customer. (BSP or others etc)

---

Best regards,

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.