Hello Ti Team,

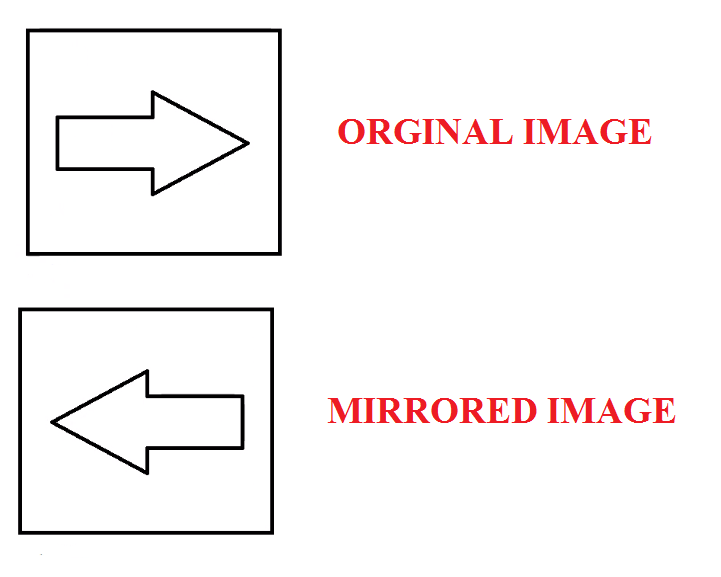

We have below usecase and we have two cameras which use Capture links as shown below. With existing usecase can we perform MIRROR Imaging, Please also see the attached Image.

If yes, Can you please share the detailed information on how to perform this

UseCase: weston_dualcamera_dsswb

Capture -> Display_Video

Capture_1 -> Display_Video1

DispDistSrc_gfx -> Display_gfx

DispDistSrc_vid3 -> Display_vid3

Capture_dsswb -> Alg_SwCrc

BR,

RK