Part Number: AM625

Tool/software:

HI TI experts,

I have the below queries related to residual voltage

1. What are the causes for Residual Voltage

2. Effect of Residual Voltage on the board performance

3. Detection of Residual Voltage

Part Number: AM62A7-Q1

Tool/software:

Hi Expert,

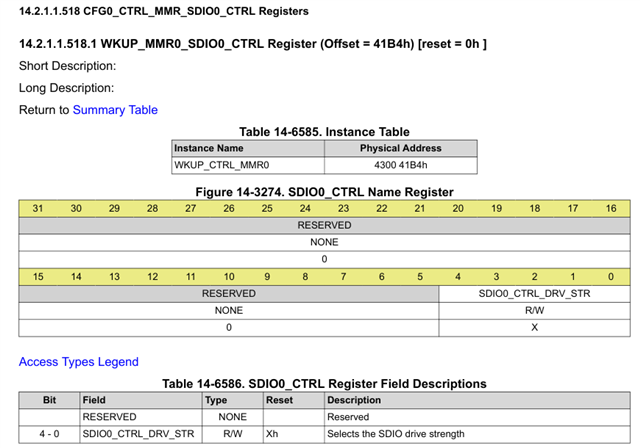

Customer was doing EMC test, it was found that the EMMC CLOCK exceeded the standard by 10dB at 1.8GHz and 1.6GHz. Can the output strength capability of the EMMC CLOCK be adjusted by below register in the figure below?

BR,

Biao

Part Number: AM6442

Tool/software:

The current Linux SDK documentation gives an example of setting up Enhancements for Scheduled Traffic (EST): https://software-dl.ti.com/processor-sdk-linux/esd/AM64X/latest/exports/docs/linux/Foundational_Components/Kernel/Kernel_Drivers/Network/CPSW-EST.html

However, the example is complicated to understand and analyze.

Is there a simpler way to test EST and analyze the results?

I am using the AM62x, AM62Ax, or AM62Px.

I want to load a different firmware into the device manager (DM) R5F core. How do I do it?

Part Number: AM62A3

Tool/software:

Hi TI experts,

I have completed my custom board schematics based on AM62Ax SOC. Could you guide me on reviewing the schematics.

Part Number: AM62P

Tool/software:

Hi TI experts,

I have completed my custom board schematics based on AM62Px SOC. Could you guide me on reviewing the schematics.

Part Number: AM6441

Tool/software:

Hi TI experts,

I have completed my custom board schematics based on AM64x or AM243x SOC. Could you guide me on reviewing the schematics.

Part Number: EDGE-AI-STUDIO

Tool/software:

Q:

“I have found TI’s model zoo with neural networks that have been validated and benchmarked on AM6xA processor [AM62A, AM67A, AM68A, AM68PA, AM69A or TDA4x SoCs] using C7x AI accelerator."

"I need to train these models for my own application with a dataset that I have collected. How do I do this?”

A:

The above is fairly common question from developers seeking to leverage pre-optimized networks from TI for their own custom application. It is suggested to use some of these models because they have already been analyzed and optimized for runtime latency and accuracy. The models available from TI are pre-trained on common datasets (e.g. COCO or Imagenet1k), but may need retraining to be applied to custom use-case.

For some networks, we have modified the original network architecture to be friendlier to the hardware accelerator used on AM6xA and TDA4x SoCs, the C7xMMA. These modifications are usually to improve accuracy or runtime efficiency on our fixed-point accelerator. For example, replacing a SiLU activation function with ReLU is far faster in fixed-point. We denote these modified architectures by including “lite” or “TI lite” in the model name within our benchmarks or model zoo repo.

With recent operator support, some original models may be supported as-is, where they were not before. Please see our list of supported operators/layers (and any related restrictions) for the latest information, and do note this documentation is version-specified with respect to our SDK.

In subsequent responses, I’ll describe and categorize models within our model zoo as it pertains to retraining and reuse.

Links and Repositories of note:

Please note I have embedded plenty of links into the text for your benefit. Most of these links will reach into the edgeai-tensorlab or edgeai-tidl-tools repositories.

TL;DR (too long, didn’t read): TI has a set of AI models that have been validated and benchmarked on our SOCs. These can be retrained, but not all architectures have a full set of examples and programming tools from TI for doing retraining yourself. In this FAQ, I’ll talk about the available resources and necessary knowledge to own this process for your design. Some architectures are modified and labelled “TI Lite” to denote that the architecture is not identical to the original version. Others are pulled by TI as-is. TI-Lite models require some optimizations that TI hard performed to be similarly done as part of training; unmodified architectures have limited support from TI for training (but compilation with TIDL tools has e2e support)

Part Number: TDA4VM

Tool/software:

How we can get the trace log information at remote cores into QNX debug terminal?

Part Number: TDA4VM

Tool/software:

The Ethernet communication on CPSW Port-8 is not successful using Native Linux Driver in SDK version 8.6 and below.