Hi TI Experts,

I have the below queries regarding use of ferrite for the SoC supply rails.

1. Do you have recommendations on using ferrite (power supply filters) for the SoC supply rails

2. Do you have some recommendations to optimize the number of ferrites used

3. I do not want to use any ferrites in my design. Do you have some recommendations

4. Are these recommendations valid for other Sitara processor

Let me know your thoughts.

Part Number: AM625

Hello,

we are currently working on a SOM based on the AM62x.

I am qualifying the MMC0 interface connected to a EMMC (SDINBDG4-8G-XI2). I have checked the datasheet of the AM62x and found this:

I only found MMC0 timing conditions for SDIO mode instead of EMMC mode.

At the AM64x datasheet i clearly find some conditions regarding the eMMCPHY, like those:

The input slew rate is clearly different from the AM64x to AM62x.

Are there no such specifications for the AM62x?

What is the PRU core? Why is it useful for applications that would typically require an FPGA or a CPLD to work?

INTRODUCTION

Many systems need to interface to an external device that does not use a standard protocol. These external devices can range from an array of analog to digital converters (ADCs) to a peripheral with a proprietary bus interface. TI’s Sitara processors with programmable real-time unit (PRU) cores are designed to communicate with these devices without the need to add FPGAs, ASICs, CPLDs, etc to the design.

.

This FAQ applies to all Sitara processors with a PRU subsystem, including AM243x, AM263x, AM335x, AM437x, AM57x, AM62x, AM64x, AM65x. For more information about the PRU, reference the PRU Development section of the Sitara multicore development and documentation FAQ.

Part Number: AM625

Hi Team,

My customer has a question about the definition of DSIS. It says the definition in the datasheet p14 as below.

Can you tell me what it means when MUXMODE is not selected? In what situations would it be not selected?

Also, can you tell me what it means by subsystem input? What signal is this referring to?

I am a little confused because my understanding is that if a specific signal is selected by MUX, then the DSIS does not matter, but it seems that from the Pin Attributes chart that for specific signals with TYPE=I, IO then there is some signal for DSIS?

Please clarify.

Best regards,

Mari Tsunoda

Part Number: AM3352

Hi,

I read on the forums (https://e2e.ti.com/support/processors-group/processors/f/processors-forum/166910/am335x-efuse-mac-ids-always-valid/609758#609758) that any AM335x device has either 2 or 3 MAC addresses programmed to them. According to the linked thread it is only ZCZ packages with PRU-ICSS that have 3, all other have 2 MAC addresses.

In a very limited test run on my end I have checked the configuration on a ZCE packaged AM3352 (i.e. no PRU-ICSS) and can see that 3 address are flashed. I know this as the macid0 is signifying the lower range and that macid1 is the higher range of assigned MAC addresses.

macid 0: b8:80:4f:ec:81:72

macid 1: b8:80:4f:ec:81:74

Can you confirm that actually all AM335x devices (or at least ZCE packaged AM3352) have 3 MAC addresses assigned and that it will continue to be that way?

Best regards

Måns

Part Number: AM69

I want to use the CAN interfaces can0, can1, can2 and can3 from Linux user space and hence want hardcode the IDs.

Currently based on the probe sequence from the Kernel, these get assigned randomly.

I tried using aliases in the Kernel Device Tree, but this doesn't help.

aliases {

can0 = &main_mcan16;

can1 = &mcu_mcan0;

can2 = &mcu_mcan1;

can6 = &main_mcan6;

can7 = &main_mcan7;

};Part Number: AM64x/AM62x/AM62Ax

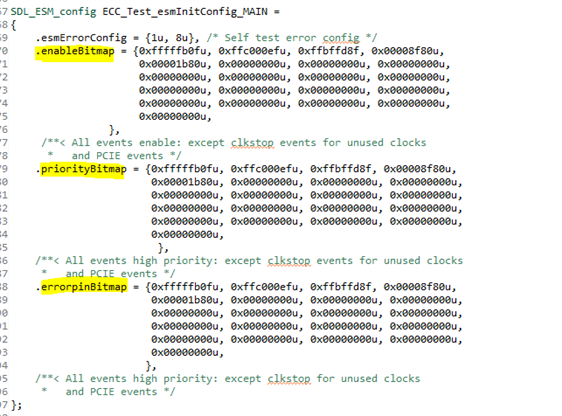

This FAQ mainly explains how to configure the ESM module in the SDL and enabling the error events which trigger the ESM interrupts.

It also shows how to set a interrupt priority for an ESM event and enable an external error pin for the corresponding event.

The below explanation would be applicable for AM64x,AM62x and AM62Ax devices.

Part Number: J721EXSOMXEVM

There is a known errata for J721E/TDA4VM/DRA829 where connecting a PCIe switch, or multi-function PCIe device would cause a system abort. This issue only affects J721E/TDA4VM/DRA829 and does not affect similar devices such as TDA4VH/TDA4VL. For convenience, posting errata documentation, of which errata i2086 is of interest: https://www.ti.com/lit/er/sprz455d/sprz455d.pdf

Logs would look like the following:

As multi-function PCIe devices and PCIe switches are common, how can we work around this errata?

Part Number: TDA4AL-Q1

Hi,

Can you provide patch to fix the issue on SDK 8.6 ?

Regards

Tarun Mukesh

How do I bring/brought up Ethernet interfaces for Main Domain CPSWnG in Linux from SDK Version 9.0 and above?