Part Number: AM623

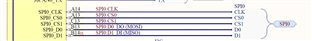

SPI data pins are named as D0 and D1. Where can i find information about the usage regarding in/output or which one is MISO / MOSI?

Part Number: TDA4VL

I want to use RGMII on MAIN_CPSW2G of TDA4VL. The link is up, but I am not able to establish a communication. I can see that Rx is working but Tx is not working.

I am using RPMsg to communicate from Linux with a remote core running RTOS (e.g., R5F or M4F). I want to define multiple RPMsg endpoints in my remote core software. How do I do that?

.

This FAQ applies to AM62x, AM62A, AM64x, AM65x, and probably other devices. The provided sample code was written for AM64x R5F, and tested on Processor SDK 8.6. The concepts will apply to all processors that use RPMsg to communicate between a Linux core and an RTOS remote core, but some of the details may change between cores and devices.

.

For other FAQs about multicore subjects, please reference Sitara multicore development and documentation

UPDATE January 2024: The information in this FAQ has been added to the processor academy modules. This FAQ will not be maintained going forward.

Please find the latest information in the processor's academy > Multicore module > Multicore Development > How to develop with RPMsg IPC > How to add multiple RPMsg endpoints to a remote core running RTOS:

AM62x

AM62Ax

AM64x

Part Number: TMS320C6678

Hi

Please provide "DDR3 Read write test code" (or) How to do DDR3 test on C6678 EVM or K2H EVM board ?

Part Number: AM625

AM62 has interrupt routers, just like any other processor. But it also has an interrupt router called the Time Sync Router (TSR) that is designed to route an input interrupt to multiple output interrupts. What is the TSR for? The documentation is not very clear at the moment, so how do I use it?

Part Number: TMS320C6678

Hi,

How to create a EDMA PING-PONG test-code using the CSL ( Chip support Library ) package and test on C6678 EVM ?

Part Number: AM625

I am using a TI processor with a PRU subsystem. I want to add an additional interface to my processor (e.g., UARTs, SPIs, I2S, etc), or a custom protocol (e.g., parallel SPIs, proprietary bus protocol, etc). Can I use the PRU cores to implement my interface or custom protocol?

.

For additional FAQs around PRU development, reference the Sitara multicore development and documentation FAQ.

Part Number: TDA4VM

Hi,

How to do Power Benchmarking (Power consumption in Watt) for supported deep learning models (Object Detection, Classification, Segmentation) on TDA4VM SoC ?

Thanks for help.

Part Number: TDA4VM

IPC uses HW mailboxes. Which ones are used, and which ones are still available ?

Part Number: TDA4VM

How to get EB studio tool for MCAL development and If you want to run the EB Tresos Configurator for TDA4VM MCAL, a customer license is required. How can I obtain this?