Hi all,

We're developing a custom board with am3874 with 512MB composed by 4 MT41J128M8.

I'm following the link

http://processors.wiki.ti.com/index.php/EZSDK_Memory_Map#Changing_Memory_Map_For_512MB_DM814x_Board

to do the memory configuration. I've done the next changes:

1) UBOOT: arch/arm/include/asm/arch-ti81xx/ddr_defs_ti814x.h

// Two 256MB sections with 128-byte interleaved (hole in b/w)

#define PG2_1_DMM_LISA_MAP__0 0x0

#define PG2_1_DMM_LISA_MAP__1 0x0

#define PG2_1_DMM_LISA_MAP__2 0x80540300

#define PG2_1_DMM_LISA_MAP__3 0xA0540300

2) UBOOT: My custom include/config/am3874custom.h

#define CONFIG_NR_DRAM_BANKS 2 /* we have 2 banks of DRAM */

#define PHYS_DRAM_1 0x80000000 /* DRAM Bank #1 */

#define PHYS_DRAM_1_SIZE 0x10000000 /* 256 MB */

#define PHYS_DRAM_2 0xC0000000 /* DRAM Bank #2 */

#define PHYS_DRAM_2_SIZE 0x10000000 /* 256 MB */

These are the ti8148_evm.h original values changing the 1GB size for 256MB

My questions are:

1) From the link, it's not clear what the point 2) values are the correct ones. Maybe I have to define

this way??

#define CONFIG_NR_DRAM_BANKS 2 /* we have 2 banks of DRAM */

#define PHYS_DRAM_1 0x80000000 /* DRAM Bank #1 */

#define PHYS_DRAM_1_SIZE 0x20000000 /* 512 MB */

#define PHYS_DRAM_2 0xA0000000 /* DRAM Bank #2 */

#define PHYS_DRAM_2_SIZE 0x20000000 /* 512 MB */

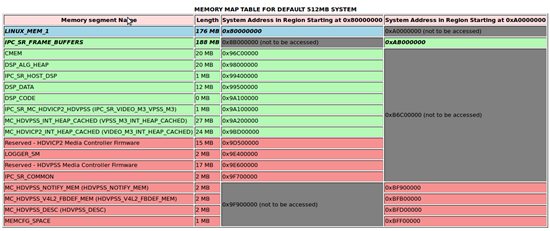

From the link image it seems that the physical memory its mapped the same in the 0x80000000 and

in the 0xA0000000 range

2) Any modification has to be done in the kernel sources?

3) What's the command line I have to set for this configuration? Is the next one correct?

setenv bootargs 'console=ttyO0,115200n8 rootwait root=/dev/mmcblk0p2 rw mem=256M ip=off noinitrd'

Any help is welcome, thanks!