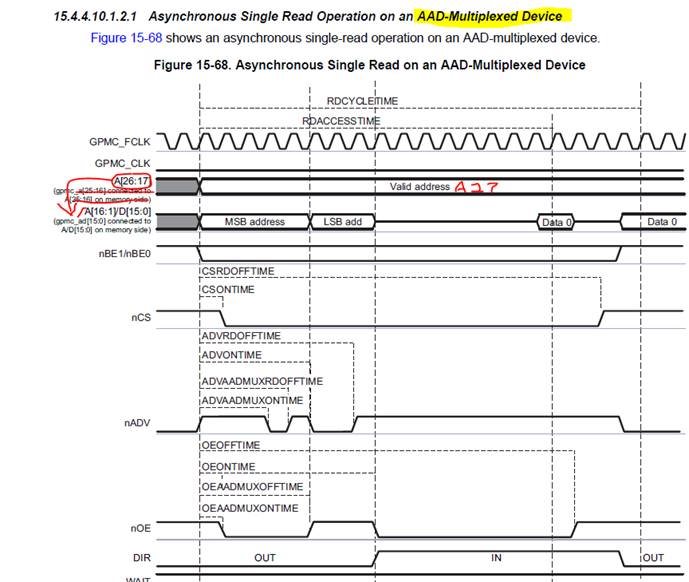

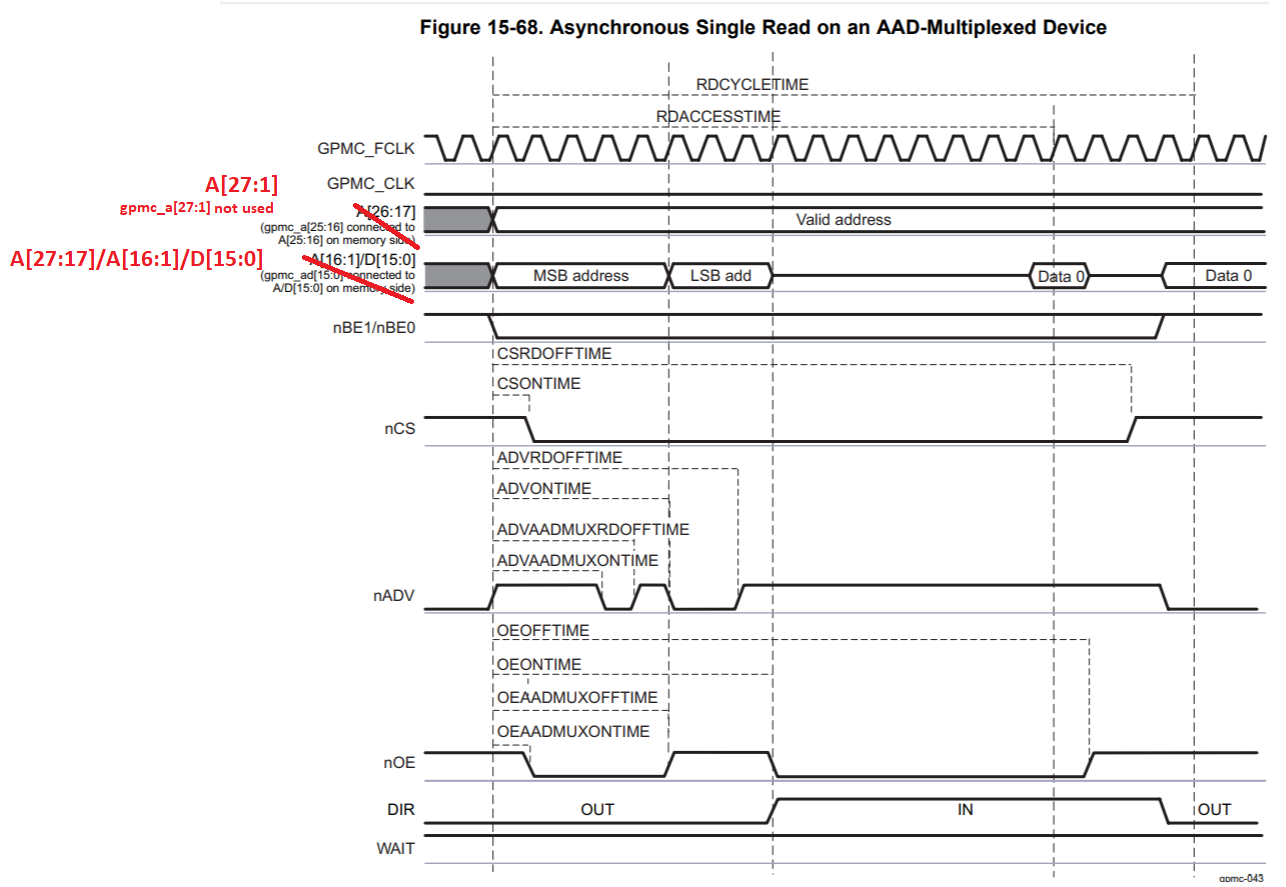

Our AM5716 application will use the GPMC parallel bus as “Multiplexed 16b NOR type” in AAD (address-address-data) mode. Does this arrangement provide all [27:1] address bits? That is, when A[MAX:17], A[16:1] D[15:0] are sequentially multiplexed onto the gpmc_ad[15:0] pins, what’s the numerical value of ‘MAX’?

The TRM timing diagrams for AAD mode show address line usage for AD mode so it’s not clear just what AAD mode address range is.