Other Parts Discussed in Thread: BEAGLEBOARD-X15

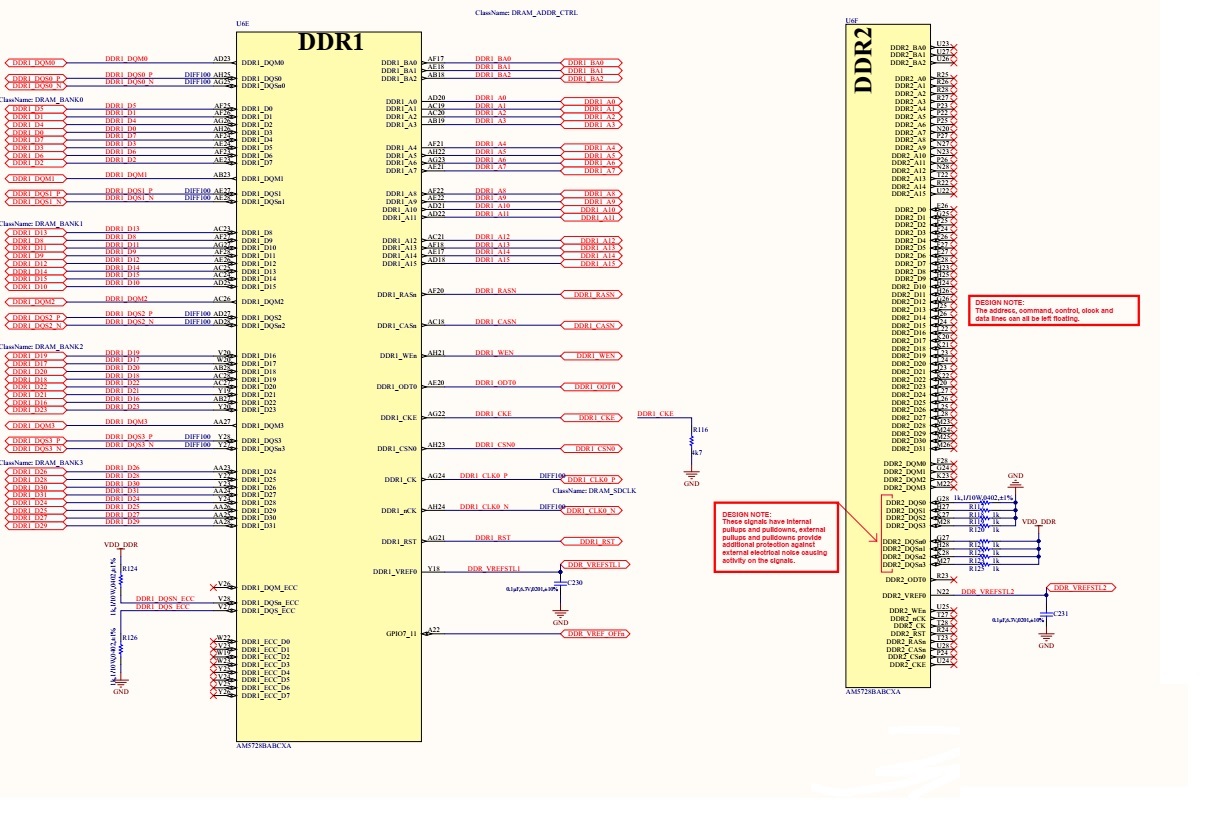

I have problems troubleshooting my custom design using AM5728. I designed by following AM572x Evaluation Board (SOM + Motherboard). The main difference from AM572x Evaluation Board, i used 2 DDR3 (16 bit) external RAM and i did not use AM5728 DDR BANK 2.

In uart boot mode, we regularly read the “VA!” message on the console from uart3. When we try to sent SPL file from UART, We observe that the package was sent from the terminal. However, after sending the package, we do not receive the 'CCC' or any message and can not proceed to the u-boot phase. Also, after sending the SPL file, we saw DDR RESET logic level became HIGH and PMIC CORE voltage changes to 1V08 from 1V15.

What is importance of DDR3 configuration on SPL boot stage? Is it possible that the DDR3 configuration be the biggest reason for the SPL boot phase not performing correctly?