Other Parts Discussed in Thread: CDCM61002

We are using the Sitara AM3874 and have some questions regarding the boot-behavior and the clock subsystem. Some boards behave in another way than others with the same hardware and software version.

In our system we are using a clock generator (TI CDCM61002) for the SERDES_CLK and PCIe_CLK. The input-reset of the CDCM is the output-reset (RSTOUT_WD_OUT) of the AM3874, only connected to a pull-up.

Comparing to boards we see that the RSTOUT_WD_OUT goes low (0V) on board 1, but on board 2 the signal on goes down to about 2.8V.

Another interesting difference between the two boards is the behaviour of PCIe_clk when only the supply of the CDCM is stable and the other supplies for the ARM are ramping up. On board 2 the pcie and serdes_clk are running and on board 1 after nPOR is released.

Question: Why are there such difference?

As described in sprugz7e 2.7.11 (and in sprs695c) the RSTOUT_WD_OUT is optional, depending on the BTMODE[11]. This BTMODE is latched when nPOR is de-asserted. We tried to change the PD/PU resistor on gpmc_ad[11], but it has no effect.

Regarding the PORz Sequence the external clocks must be stable before POR is released. As described above on board 1 the RSTOUT_WD_OUT is low -> the serdes_clk and pci_clk are also low. So the point 7 in chapter 2.7.15 “When power and clocks to the chip are stable, PORz is de-asserted” cannot be reached.

We see the internal pll don’t lock, so we have startup problems.

Question: How is it possible to disable the RSTOUT_WD_OUT assertion during an active POR ?

Edit (09/23/2020):

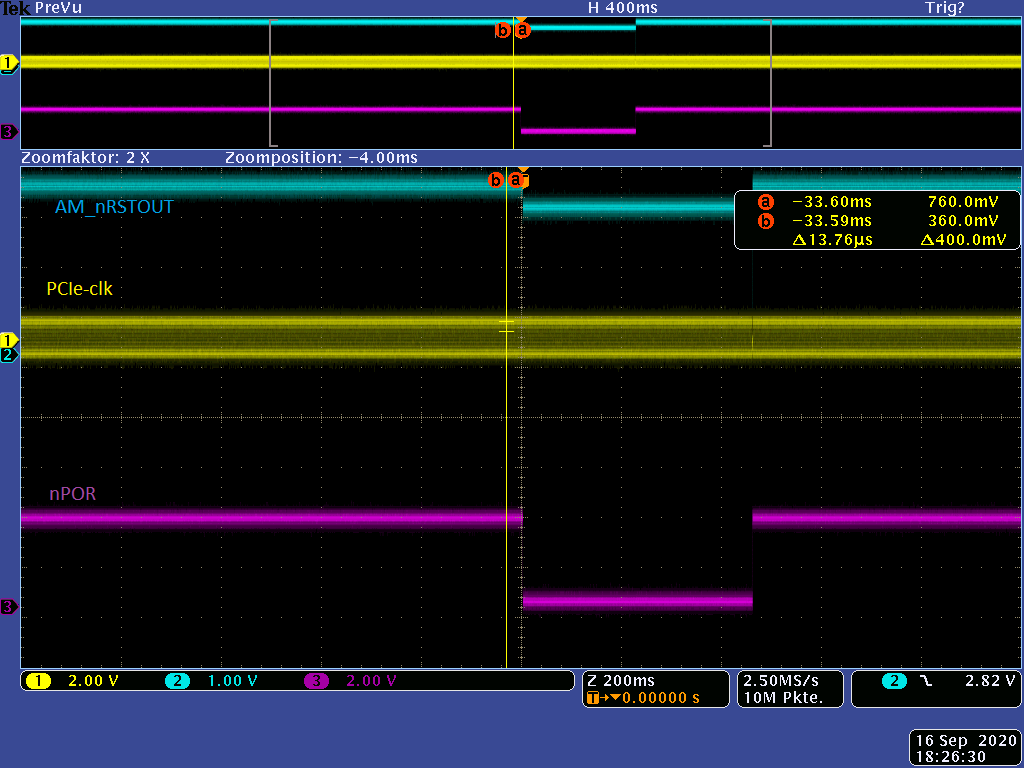

This is the behavior of the device 1. The trigger postition is about power on. We added a POR-Sequence from a connected FPGA, which also can control the signals POR, RESET(in) and GPMC_AD[*], We forced the gpmc_ad[11] to '1' until the por-signal deasserts.

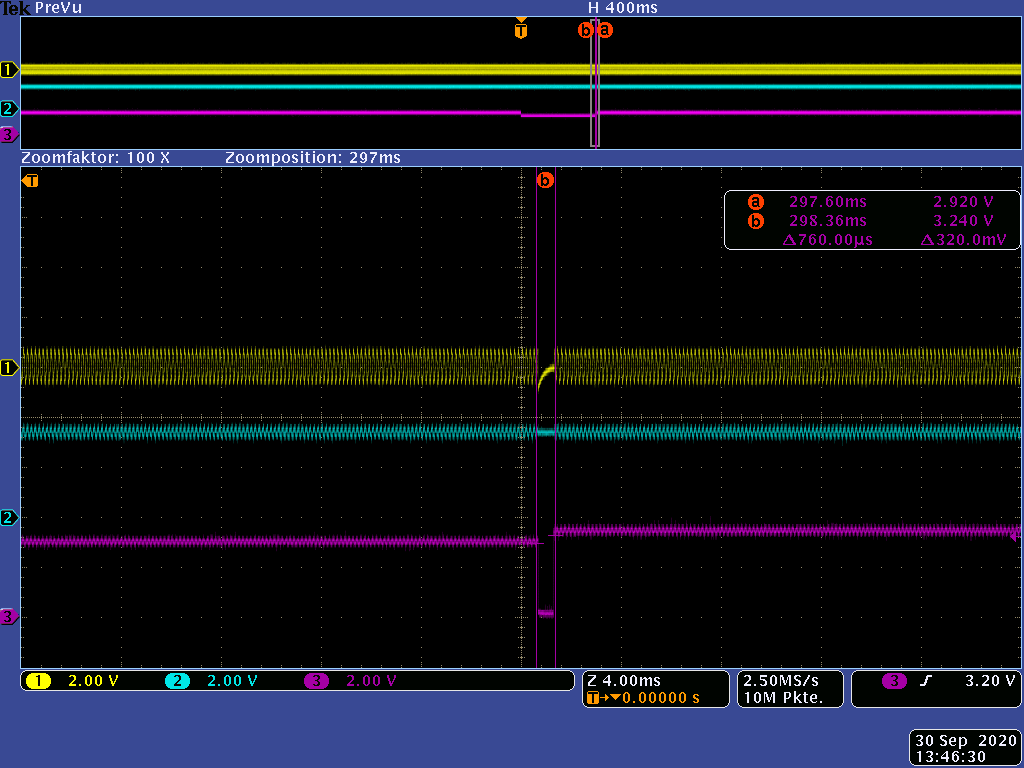

For comparision the device 2 - as you can see there is only a 0.5V-drop on the signal WD_RSTOUT (this is very confusing).

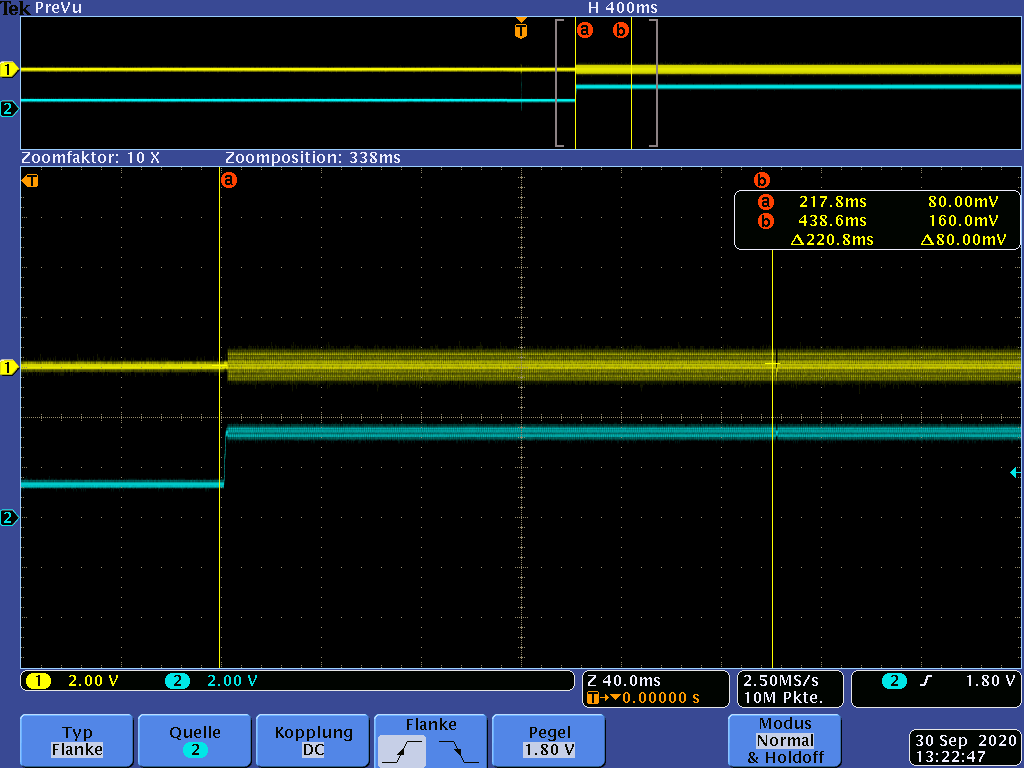

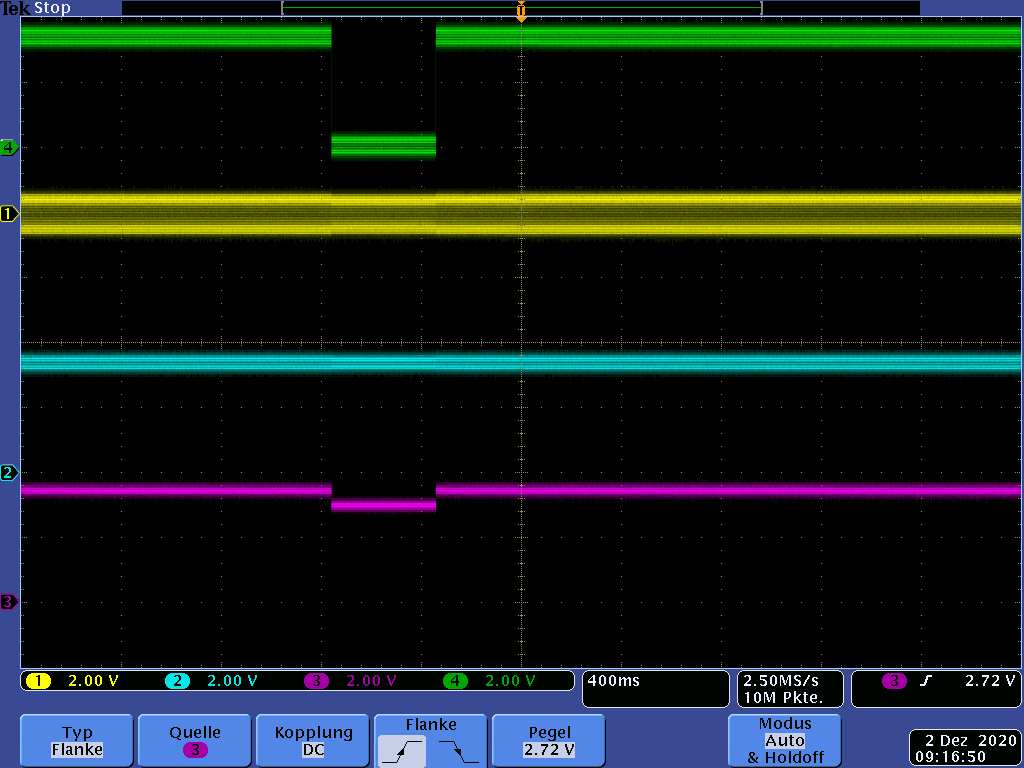

The following schematics-parts are showing the connection of the described clocks and Reset-Signal.