Hi,

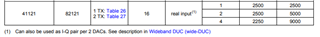

I config DAC38RF89's JESD204B as fallowing.

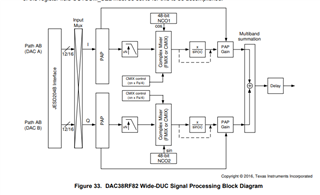

It is used as I-Q pair per 2 DACs. I use DACA, Q use DACB.

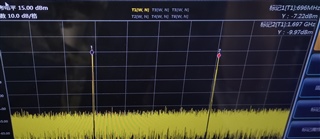

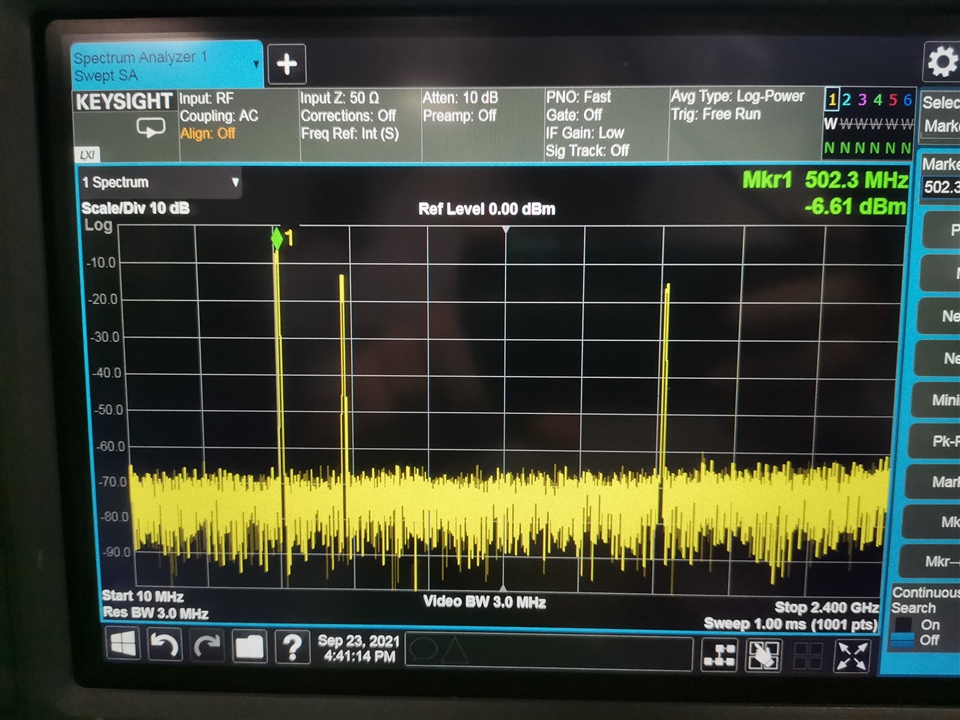

I transmit the I-Q data to the DUC input.For instance, the input frequency is 500MHz and the NCOfrequency is 1.2GHz. When I use the spectrometer to observe, there are two spectral lines with symmetry about 1.2GHz, which are 1.7GHz and 700MHz respectively.

I want to know the reason? And how can the output frequency after DUC be correct after several resets?

Regards,

Fox