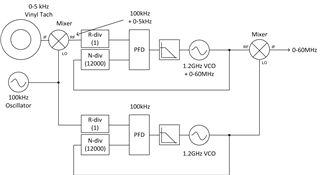

I have a free software and hardware project (RAM platter hybrid) which requires a low frequency source oscillator to have its frequency multiplied up 12000 times. It is possible that this is a good application for DDS or a VCO+PLL.

The source oscillator ranges between 0 Hz and 5 kHz. The most common rate of the source oscillator (f0) is 1 kHz.

The implication of the 12000 frequency multiplier is that the target output signal frequency is from 0 Hz to 60 MHz. Exact 0 Hz output is not necessary but desireable. Close to 0 Hz is very desirable, but 1 Hz or 10 Hz is ok.

As the platter is interfaced by a human, the source tone is extremely band limited in its ability to change. For that reason the rate of change of the source oscillator is slow. For example, a normal rate of change is limited by the speed of a persons hand moving - that may be at a rate of 1 or 2 kHz per second.

Extreme jitter control when the source oscillator is idling is not necessary as the platter is a heavy flywheel (a turntable's platter) and this should mitigate a certain amount of jitter in the source oscillator's signal. It would be an advantage however if jitter reduction was possible.