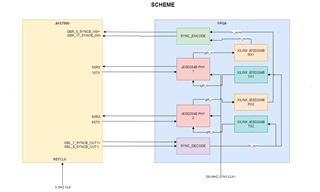

Figure1.

I have a custom board design with AFE7900 and Xilinx Xcku050 FPGA.

Figure 1 shows that the FPGA-AFE connection in my design.

All Xilinx JESD204 IP are configured as LMFS=1-4-8-1-0, K=4, and LaneRate=10 Gbps. core_clk frequency is 250 MHz.

I wanted to configure AFE7900 2-link 1-4-8-1-0 configuration. Lane Rate is 10 Gbps.

After FPGA starts the configuration steps which are created in Latte Scripts. (it's in attached files.)

I check the Xilinx IP gt0_rx signals in ILA but I haven't seen the h'BCBCBCBC in gt0_rx signals.

Because of that the FPGA RX IP's don't complete the SYNC process.

Why the FPGA does not catch the h'BCBCBCBC characters in SERDES line?

I don't know how to debug this.

Could you give me advice on this problem?

Best Regards.

Stsecen