Part Number: AFE7799

Other Parts Discussed in Thread: AFE7769

Hi expert,

Customer used AFE7799 and when they did 100 times reboot test, there is chance to see JESD204B link failed. Some questions and debug process would like to consult with you,

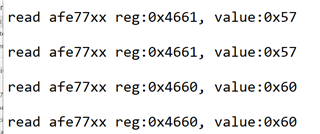

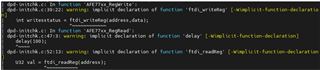

- How to check the AFE7799 JESD 204B RX status by SPI command?

- How to reset the AFE7799 JESD 204B TX by SPI command?

- How to reset the AFE7799 JESD 204B RX by SPI command?

- is it a right approach and how to use Tx signal loopback to Rx/Fb then to let FPGA check the Rx/Fb path signal quality?

Regards,

Allan