i'm bringup afe7920 with xilinx zynqmp.

In latte, we got the settings we wanted and

ZYNQMP wrote the settings to the AFE7920 via SPI.

But the data coming from the AFE7920 to the FPGA is unchanged.

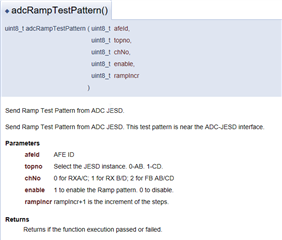

So I wanted to send something like a test pattern from AFE7920 via SPI settings and when I looked at the register map, I found the following registers.

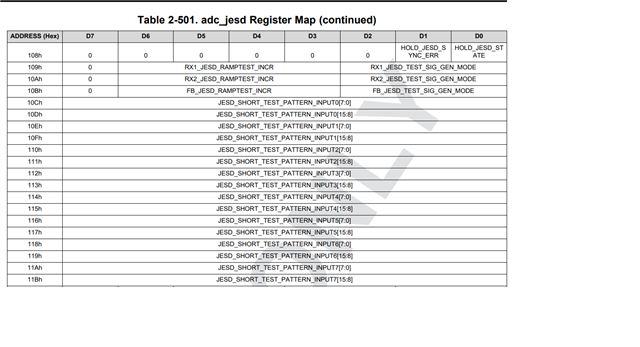

If you look at the ADC register map, you will see the registers for the test pattern from 109 to 11B.

So I set the values as below and did not see any change in the values when viewed through FPGA ILA.

Is there something I am missing or setting incorrectly?

write 0016 01

write 010c 01

write 010d 12

write 010e 34

write 010f 56

write 0110 78

write 0111 9a

write 0112 bc

write 0113 de

write 0114 f0

write 0115 10

write 0116 32

write 0117 54

write 0118 76

write 0119 98

write 011a ba

write 011b ed

write 0109 01 or 02

write 010a 01 or 02

write 010c 01 or 02

write 0016 02

write 010c 01

write 010d 12

write 010e 34

write 010f 56

write 0110 78

write 0111 9a

write 0112 bc

write 0113 de

write 0114 f0

write 0115 10

write 0116 32

write 0117 54

write 0118 76

write 0119 98

write 011a ba

write 011b ed

write 0109 01

write 0109 01 or 02

write 010a 01 or 02

write 010c 01 or 02