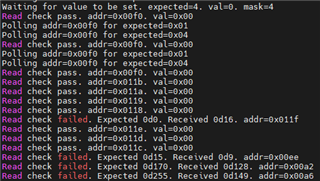

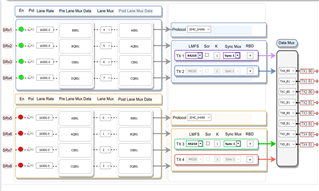

We have a custom design with an AMD Versal connected to a TI AFE7950. The Versal contains an AMD JESD204C Transmit core, which we are sending IQ sine/cosine data from a LUT. The issue is that it appears to have a 50/50 chance of coming up without any errors during the AFE configuration, but the other half of the time I see multiple alarms and errors that seem to be consistently related to a bad RBD value.

The RBD value generated from Latte (shown below) is 4. I ran through the calculation documented in TI SBAA543 from reading the lane counters, which all read back as 0: RBD = (0 + 4) % (64 *1) = 4 % 64 = 4

The calculated RBD value appears to match the value from Latte, though the intermittent link initialization failures seem to indicate a bad RBD value. I was curious if you had any suggestions on how to debug/investigate further.

We have done PRBS31 link testing between the FPGA and AFE at 16.5 Gbps using AMD's IBERT tools, and did not see any errors detected. The captured eyes also looked good.

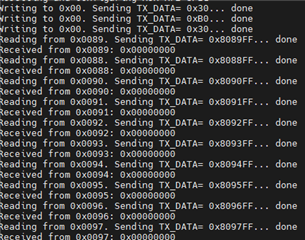

The other question I had is if you had the SPI commands to run the CAFE adcDacSync command? I see it referenced, but we don't have a direct connection to the AFE and PC, so we are sending SPI commands via the FPGA.