Tool/software:

Hello,

I am running the output of a Latte log with an AFE7950 using not continuous sysref and am getting a couple of errors due to MACRO_DONE not getting set after running a MACRO at two different points in the code. The MACRO opcodes are not documented and I can't tell from the comments what is being attempted with the MACROs.

Here's an excerpt for the first case of MACRO_DONE not getting set (lines 1718-1737):

SPIRead 00f0,0,0

//Read MACRO_READY=0x1; Address(0xf0[7:0])

SPIPoll 00f0,0,0,01

SPIWrite 00a3,00,0,7 //MACRO_OPERAND_REG0=0x1; Address(0xa0[7:0],0xa1[7:0],0xa2[7:0],0xa3[7:0],0xa4[7:0])

SPIWrite 00a2,00,0,7

SPIWrite 00a1,00,0,7

SPIWrite 00a0,01,0,7

SPIWrite 0193,78,0,7 //MACRO_OPCODE=0x78; Address(0x193[7:0],0x194[7:0])

WAIT 0.001

SPIRead 00f0,2,2

//Read MACRO_DONE=0x1; Address(0xf0[7:2])

SPIPoll 00f0,2,2,04

SPIReadCheck 00f0,3,3,00

The final SPIReadCheck fails. Any idea why MACRO_OPCODE=0x78 would not complete?

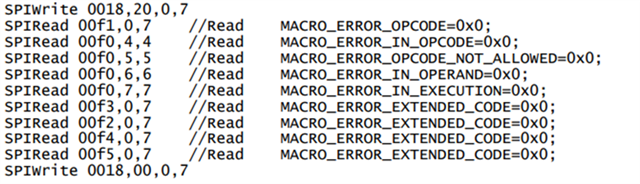

If I comment out the failing SPIReadCheck, the code can make it to later in the programming, where a similar error occurs, but for a different MACRO_OPCODE.

Here's the excerpt (lines 3529-3551):

//START: Configuring TX Chain Parameters to TOP MCU

SPIWrite 0018,20,0,7 //macro=0x1; Address(0x18[7:5])

SPIRead 00f0,0,0

//Read MACRO_READY=0x1; Address(0xf0[7:0])

SPIPoll 00f0,0,0,01

SPIWrite 00a3,00,0,7 //MACRO_OPERAND_REG0=0x1; Address(0xa0[7:0],0xa1[7:0],0xa2[7:0],0xa3[7:0],0xa4[7:0])

SPIWrite 00a2,00,0,7

SPIWrite 00a1,00,0,7

SPIWrite 00a0,01,0,7

SPIWrite 0193,8d,0,7 //MACRO_OPCODE=0x8d; Address(0x193[7:0],0x194[7:0])

WAIT 0.001

SPIRead 00f0,2,2

//Read MACRO_DONE=0x1; Address(0xf0[7:2])

SPIPoll 00f0,2,2,04

SPIReadCheck 00f0,3,3,00

The final SPIReadCheck gives an error. Any idea why MACRO_OPCODE=0x8d would not complete?

If I comment out the two failing SPIReadCheck, the scripts completes, but I see some kind of random misalignment in the lanes, from power cycle to power cycle. I'm using LMFS=8821 with the TI JESD204C IP. When transmitting a test complex sine wave, I see two tones of different amplitudes at +/- the expected offset frequency from the NCO frequency. Occasionally, one of the 4 DACs has a good output (single offset tone), but across power cycles, the bad behavior occurs randomly on different DAC channels. I am wondering if the failing MACROs could account for this strange behavior.

Thanks for any help or suggestions!