Part Number: AFE7950

Tool/software:

Dear TI Team,

I am currently working on a setup involving the AFE7950EVM, where I aim to generate a 1 GHz sine wave, send it to the DAC, and process the looped-back ADC data via the FPGA JESD interface. I have a few queries and would greatly appreciate your assistance in resolving them:

-

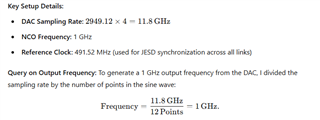

DAC Sampling Rate:

The DAC sampling rate displayed in the Latte GUI is mentioned as2949.12 * 4 = 11,796.48 MSPS. Could you please explain why this multiplication by 4 is performed? and I can change or not how? -

Frequency Calculation for Custom Sine Wave (64-point LUT):

I calculated the sine wave frequency as184.32 MHz(clock) / 64(point) = 2.88 MHzbased on the customized 64-point sine wave generated from thesine_64point.vVerilog code. Is this the correct frequency? If not, could you clarify the expected frequency? given 64 point Verilog code? -

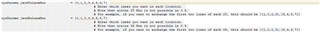

NCO Frequency Configuration:

sysParams.txNco0 = [[1000,1000], # Band0, Band1 for TxA for NCO0

In the Latte GUI, I modified the NCO frequency using the following configuration:

[1000,1000], # Band0, Band1 for TxB for NCO0

[1000,1000], # Band0, Band1 for TxC for NCO0

[1000,1000]] # Band0, Band1 for TxD for NCO0

-

Are there additional configurations I need to ensure proper operation, or is this sufficient?

-

SYSREF and Reference Clock:

I have connectedsysref_pandsysref_nfrom the AFE7950EVM to the FPGA. The system clock (sys_clock) is set to 184.32 MHz, as specified by the EVM.wire sysref; IBUFDS sysref_ibuf (.I(sysref_p), .IB(sysref_n), .O(sysref)); assign rx_sysref = sysref; assign tx_sysref = sysref;Could you confirm the reference clock (ref clock) frequency from the AFE7950?

-

JESD Data Rate and Sampling Rates:

After processing through the JESD interface, what is the expected data rate? How is this data rate related to the ADC and DAC sampling rates? -

1 GHz Sine Wave LUT:

Could you provide a LUT or samples data for generating a 1 GHz sine wave using the AFE7950 DAC?

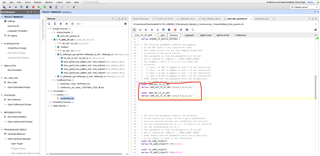

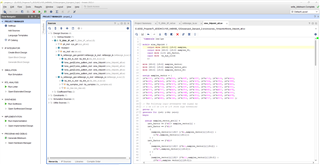

gui

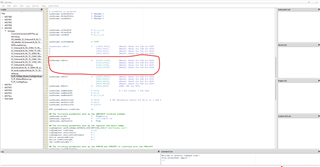

verilog code

I have connected the DAC output to the ADC input via RF cable (J9 to J3) on the AFE7950EVM. I look forward to your guidance to ensure proper configuration and understanding of the data flow.

Thank you.

Best regards,

Banoth Balu