- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Team,

During testing of the AFE7950EVM board, we encountered an issue with the output signal from the DAC.

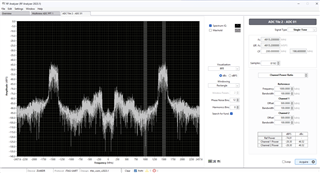

We are transmitting a 10 MHz signal from the ZCU106 FPGA to the AFE7950EVM DAC TXA and TXB channel via JESD204, with an NCO frequency of 1.5 GHz. However, upon analyzing the signal with an RF analyzer, we observed an LFM (Linear Frequency Modulation) signal.The captured signal is shown in the attached figure below.

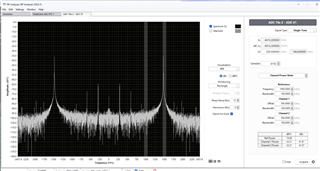

And When transmitting a DC value from FPGA to the AFE7950EVM DAC TXA and TXB channel via JESD204B, with an NCO frequency of 1.5 GHz. We observed the frequency output of 1.5GHz on the RF analyzer. The captured signal is shown in the attached figure below.

Additionally, we have executed the script on the AFE7950EVM board, which is also included below.

#fpgaside 24410 afeside 12410 1 inst's are there

############## Read me ##############

#In HSDC Pro DAC tab, Select AFE79xx_2x2TX_44210; Data Rate = 245.76M

#In HSDC Pro ADC tab, Select AFE79xx_2x2RX_44210; Data Rate = 245.76M ---> To capture 4 RX channels

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 # setup FPGA (TSW14J56) using HSDC Pro

############## Top Level ##############

sysParams.FRef = 491.52

sysParams.FadcRx = 2949.12

sysParams.FadcFb = 2949.12

sysParams.Fdac = 2949.12*4

sysParams.externalClockRx=False

sysParams.externalClockTx=False

############## Digital Chain ##############

##### RX #####

sysParams.ddcFactorRx = [12,12,12,12] #DDC decimation factor for RX A, B, C and D

sysParams.rxEnable = [True,True,False,False]

sysParams.rxNco0 = [[1500,1500], #Band0, Band1 for RXA

[1500,1500], #Band0, Band1 for RXB

[1500,1500], #Band0, Band1 for RXC

[1500,1500]] #Band0, Band1 for RXD

##### FB #####

sysParams.fbEnable = [False,False]

sysParams.ddcFactorFb = [12,12] #DDC decimation factor for FB 1 and 2

sysParams.fbNco0 = [9500,9500] #Band0 for FB1 and FB2

##### TX #####

sysParams.ducFactorTx = [48,48,48,48] #DUC interpolation factor for TX A, B, C and D

sysParams.txEnable = [True,True,False,False]

sysParams.txNco0 = [[1500,1500], #Band0, Band1 for TXA

[1500,1500], #Band0, Band1 for TXB

[1500,1500], #Band0, Band1 for TXC

[1500,1500]] #Band0, Band1 for TXD

############## JESD ##############

##### ADC-JESD #####

sysParams.jesdSystemMode= [3,3]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; rx -rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb -fb- fb -fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol= [0,0] # 0 - 8b/10b encoding; 2 - 64b/66b encoding

sysParams.LMFSHdRx = ["24410","24410","24410","24410"] #changed by Lakshmi ["44210","44210","44210","44210"]

# The 2nd and 4th are valid only for jesdSystemMode values in (0,2).

# For other modes, select 4 converter modes for 1st and 3rd.

sysParams.LMFSHdFb = ["24410","24410"]

sysParams.rxJesdTxScr = [True,True,True,True]

sysParams.fbJesdTxScr = [True,True]

sysParams.rxJesdTxK = [16,16,16,16]

sysParams.fbJesdTxK = [16,16]

sysParams.jesdTxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2T,

# this should be [[1,0,2,3],[5,4,6,7]]

sysParams.serdesTxLanePolarity = [1,1,0,0,0,0,0,0] ########## newly added

sysParams.jesdTxRbd = [2, 2] ########## newly added

##### DAC-JESD #####

sysParams.jesdRxProtocol= [0,0]

sysParams.LMFSHdTx = ["24410","24410","24410","24410"]

sysParams.jesdRxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

sysParams.serdesRxLanePolarity = [1,1,0,0,0,0,0,0] # For example, if you want to exchange the first two lines of each 2R

# this should be [[1,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd = [2, 2] ########## changed

sysParams.jesdRxScr = [True,True,True,True]

sysParams.jesdRxK = [16,16,16,16]

##### JESD Common #####

sysParams.jesdABLvdsSync= False

sysParams.jesdCDLvdsSync= False

sysParams.syncLoopBack = True #JESD Sync signal is connected to FPGA

############## GPIO ##############

sysParams.gpioMapping = {

'H8': 'ADC_SYNC0',

'H7': 'DAC_SYNC0', #'ADC_SYNC1',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'ADC_SYNC1', #'DAC_SYNC0',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

############## LMK Params ##############

lmkParams.pllEn = True

lmkParams.inputClk = 983.04 # Valid only when lmkParams.pllEn = False

lmkParams.lmkFrefClk = True

setupParams.fpgaRefClk = 245.76 # Should be equal to LaneRate/40 for TSW14J56

############## Logging ##############

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x21 #Modify to 0x1 to save register scequence to log file. Script takes more time to execute.

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#--------------------------------------#

setupParams.skipLmk = False

AFE.initializeConfig()

lmkParams.sysrefFreq = AFE.systemStatus.sysrefFreq

lmkParams.lmkPulseSysrefMode = False

AFE.LMK.lmkConfig()

## Initiates AFE79xx Bring-up setupParams.skipLmk = True AFE.deviceBringup() AFE.TOP.overrideTdd(15,3,15)

Could you kindly provide some insights or guidance on this behavior?

Thanks

Hi Ajay,

When running the bringup do you receive any JESD errors? One suspect for the issue you are seeing is a lane polarity issue. For the lane polarity you would need to verify the schematics but i believe it should be 'sysParams.serdesRxLanePolarity = [1,1,1,1,0,0,0,0]' for the ZCU106 to AFE7950EVM. Can you try updating this in your script and see if this solves your issue?

Regards,

David Chaparro