Other Parts Discussed in Thread: DCA1000EVM, AWR1243

Hello Team,

Posting on behalf of my customer:

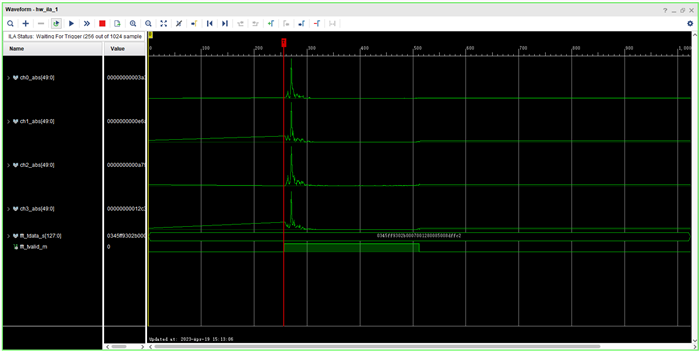

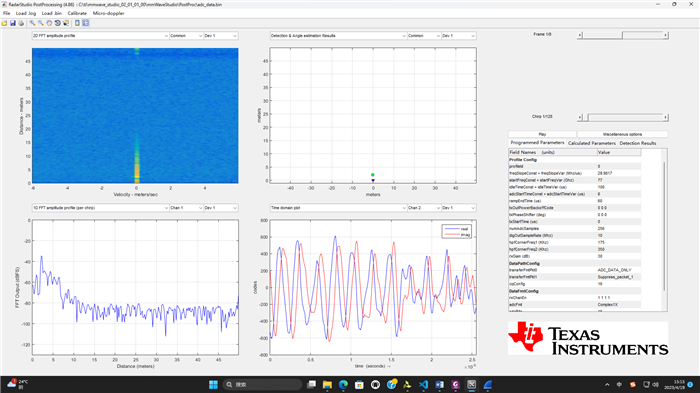

I have AWR1243 module and DCA1000EVM module, and plan to use them for real-time transmission of radar data to FPGA development board.

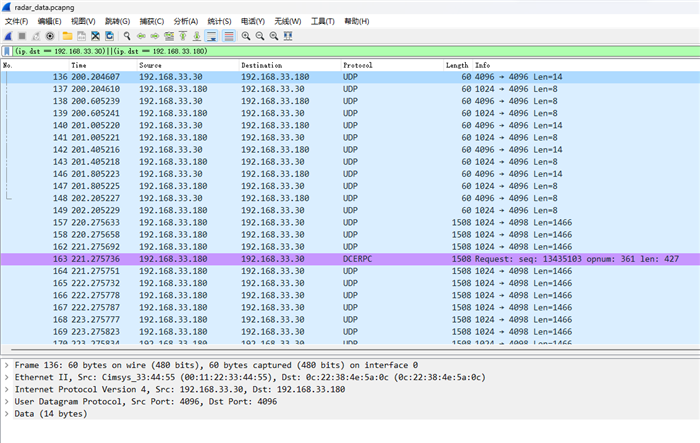

I found that in the packets sent back by DCA1000EVM, a DCERPC packet will appear every 256 UDP packets, and the order of this DCERPC packet will always be in the 4th of 256 packets, and the data length of both UDP packet and DCERPC packet is 1466 bytes.

Question 1: Could you mind tell the meaning of the DCERPC packets. Do they have a special meaning compared to UDP packets? Do they both contain 1456 bytes of Raw mode data?

Question 2: During the experiment, I also found a Pathports packet, does the Pathports packet have a special meaning relative to the UDP packet? Do they both contain 1456 bytes of Raw mode data?

Regards,

Renan