Other Parts Discussed in Thread: , UNIFLASH

Hi,

this thread didn't help me.

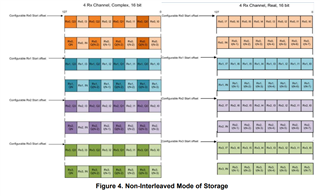

Referring to the Data Path User Guide , the non-interleaved complex data or real data in the adcbuf memory of IWR6843 is stored as:

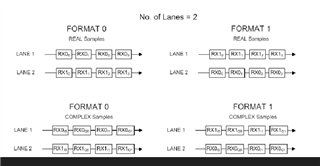

and the output on LVDS in Non-interlaleaved mode for 2 data lanes can be :

data lane 0 | rx0_sample0_real | rx0_sample0_imag| ... | rx0_sampleN-1_real | rx0_sampleN-1_imag |...| rx1_sample0_real | rx1_sample0_imag| ...

data lane 1 | rx0_sample1_real | rx0_sample1_imag| ... | rx0_sampleN_real | rx0_sampleN_imag |...| rx2_sample0_real | rx2_sample0_imag| ...

or

data lane 0 | rx0_sample0_real | ... | rx0_sampleN_real |...........| rx4_sample0_real |...| rx4_sampleN_real | ...

data lane 1 | rx0_sample0_imag | ... | rx0_sampleN_imag |............| rx4_sample0_imag |...| rx4_sampleN_imag | ...

my Questions are:

Is it possible the configure IWR6843 so that the output of Data on the LVDS lanes are macthing with the second on?

Is yes, how to set it ?

Best Regards,

joseph