Other Parts Discussed in Thread: DRV5033

Hi,

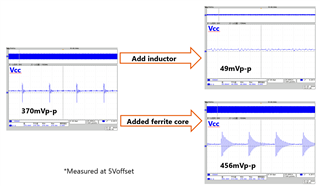

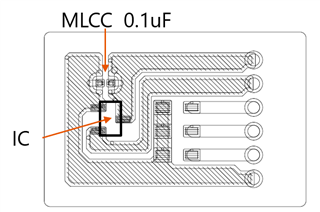

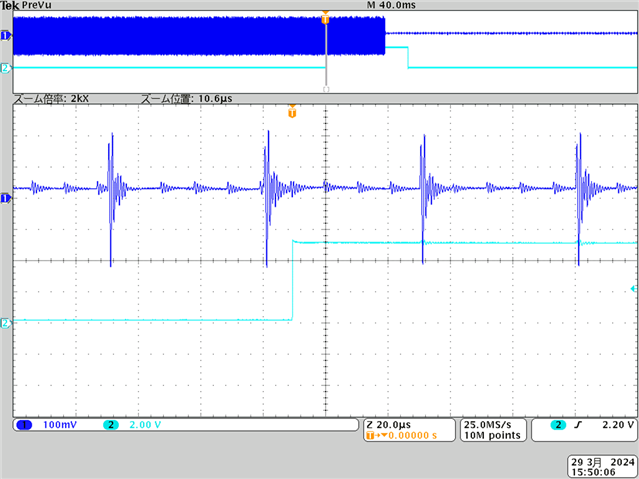

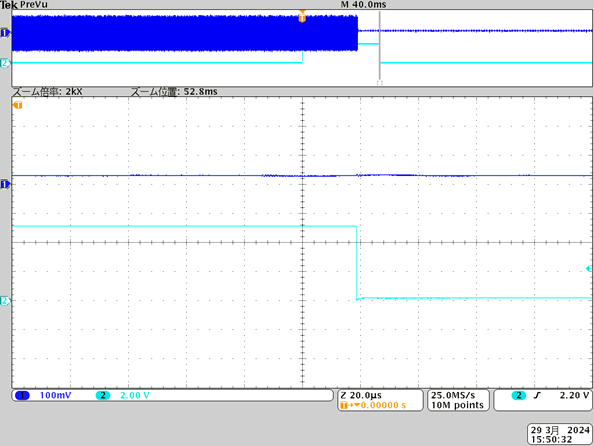

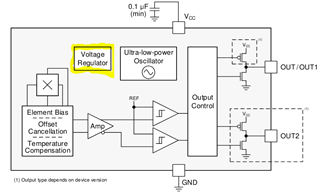

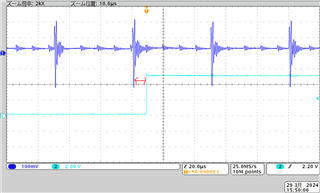

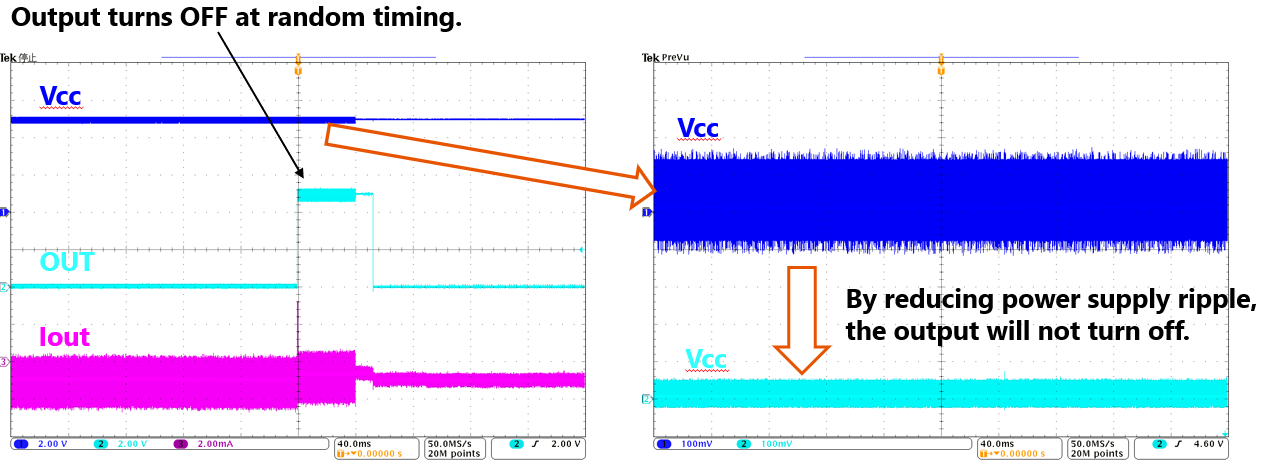

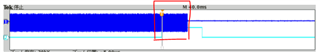

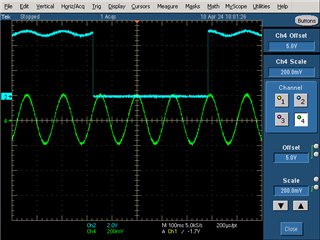

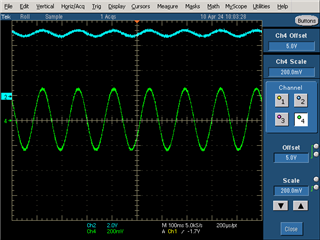

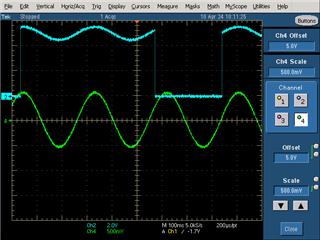

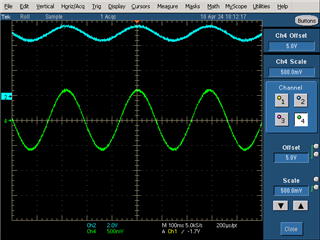

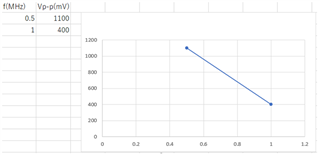

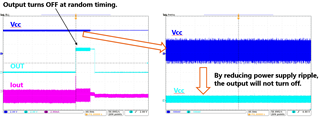

I'm having a problem with DRV5032FA. Even though the positions of the magnet and Hall IC have not been changed, a signal indicating that the magnet is not detected is output at random times, and then a normal signal (magnet detected) is output. When reduce the ripple on the DRV5032FA's power pins, this problem will no longer occur. Could you please confirm the cause of this problem ?

I also investigated E2E and found the following thread.

It is stated in the thread that this is a problem with DRV5033 and does not occur with DRV5032. However, the same problem is occurring with DRV5032FA, so could you please give me some comments?

Thanks,

Conor