Hi,

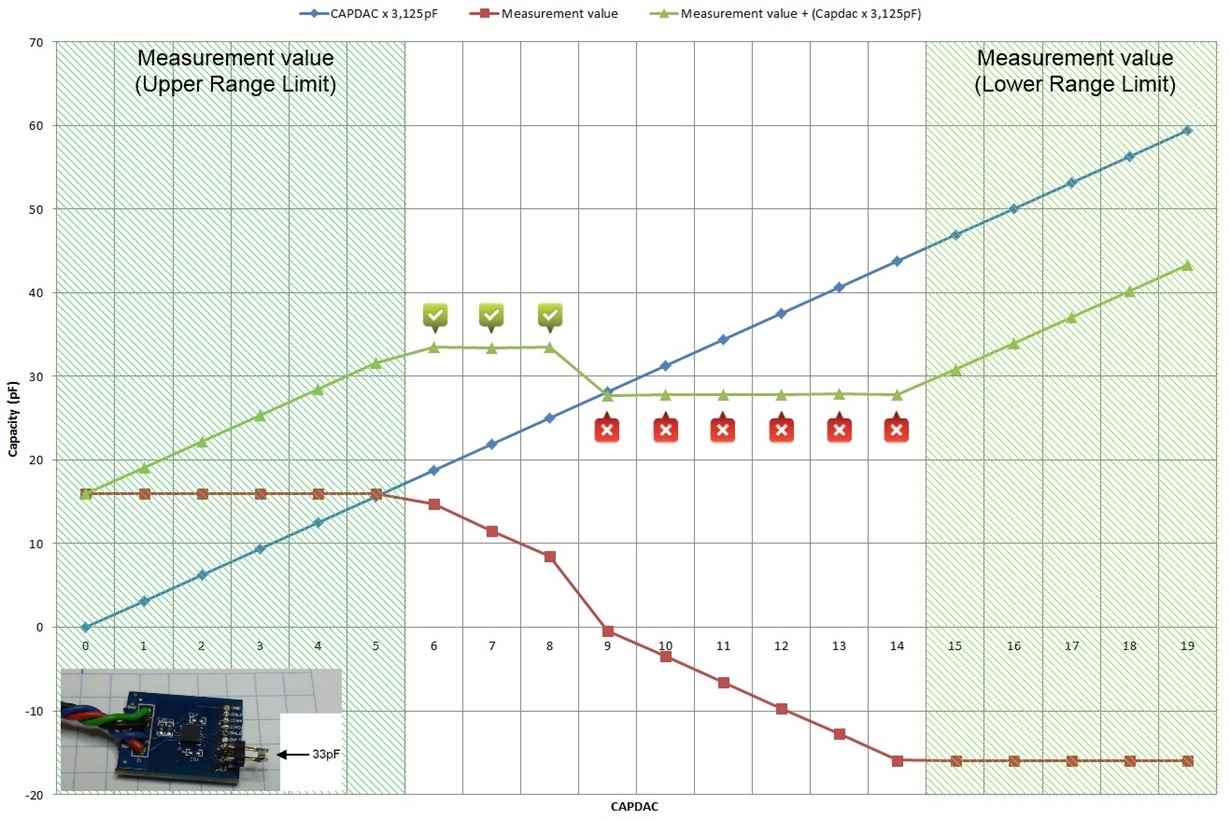

Am doing basic capacitance test with FDC1004.

39pF input am giving to FDC1004. The output scenario follows,

1) Coffset = 25.0 and read capacitance from capacitive measurement registers is 13.968pF. The output is 13.968+25.0=38.968pF which is almost matching with 39pF.

2) Coffset = 28.125 and read capacitance from capacitive measurement registers is 4.830pF. The output is 4.830+28.125=32.955pF which is not near to 39pF.

From the above two scenarios, first one is correct. But second one is wrong. Why it's misbehaving when i change the offset from 25.0 to 28.125 eventhough input capacitance is within measurable range.