Hi there,

Could I please get some assistance about Hardware In Loop (HIL) on TI’s ECA1000 board? The progress currently is that test data from FPGA can be sucessfully written into PING buffer at 0x5200_0000 on MSS core and interrupts can also be captured on DSP side. However, one problem that turns out is that data in PING buffer and data in PONG buffer do not show up at the same time. Please see the below testing process in details:

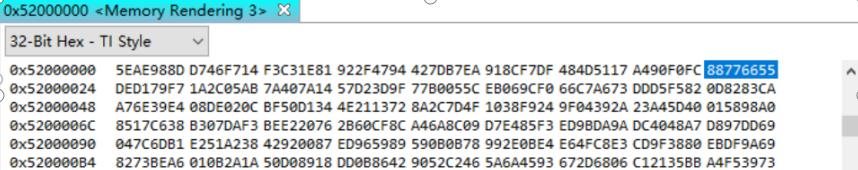

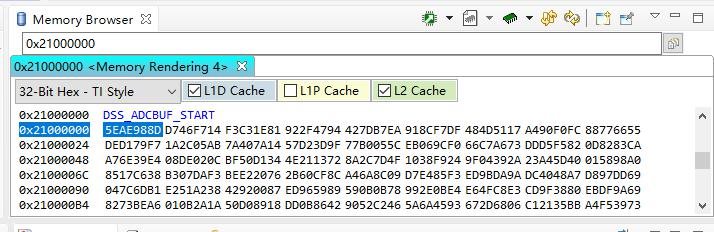

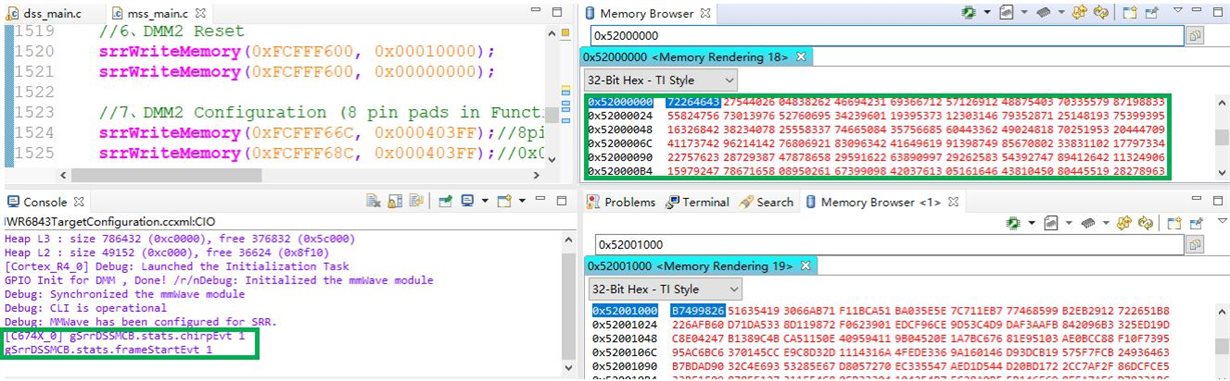

After initialization of DMM1 and DMM2 on DSP side, some randam data can be seen from starting address 0x5200_0000 (32K) and these data do not change until powering off.

Following https://e2e.ti.com/support/sensors/f/1023/t/861828#pi320995=2

The sequence we tried:

1) set to PING buffer address 0x0042_0000

2) frame start interrupt

3) write data into PING buffer

4) switch to PONG buffer 0x0063_0000

5) PING PONG interrupt

6) some delay

7) write data into PONG buffer

8) switch back to PING buffer

9) PING PONG interrupt

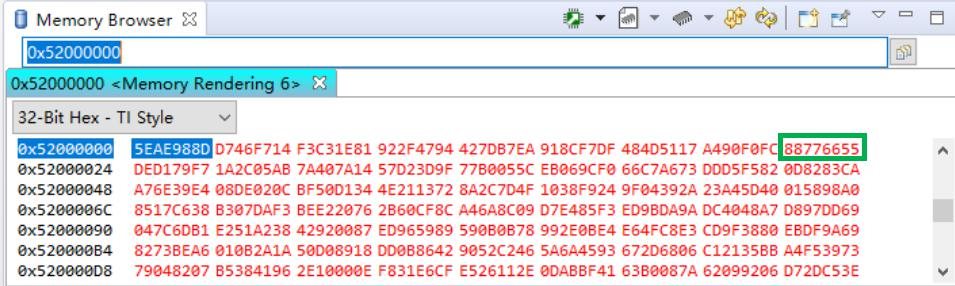

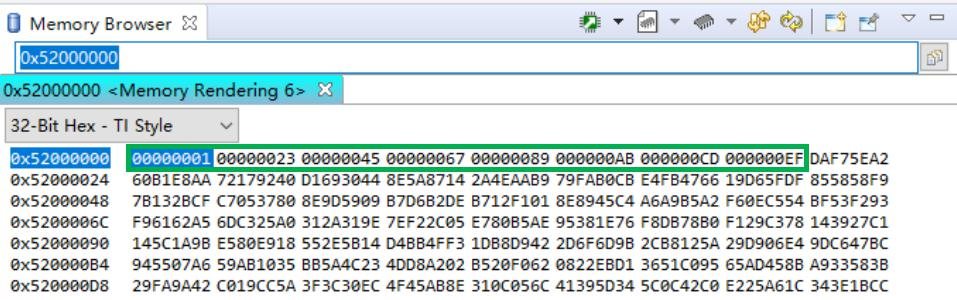

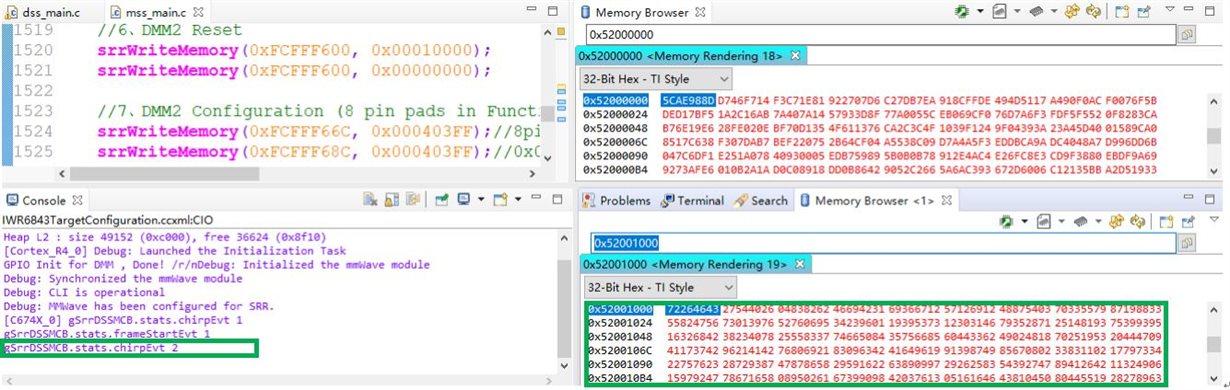

The first screen shot above gives the result of PONG buffer data change only. One interesting thing found is that the PING buffer data will actually appear after disconnecting and hardware reset. See the 2nd screen shot. Moreover, after debugging, we did capture one frame interrupt and two chirp available interrupts.

So far, our guess is that the random data which shows up at the beginning seems to be the problem. There is data from 0x5200_0000 to 0x5200_7FFF, while other address locations are ?????? (no data). These data might have higher priority which blocks us from seeing PING or PONG data at the same time.

We also tried to use copy memory command while chirp available interrupt counter reaches 1 in order to transfer PING data to other address, but it does not work.

Thanks,