Tool/software:

Hi team,

I have two questions,

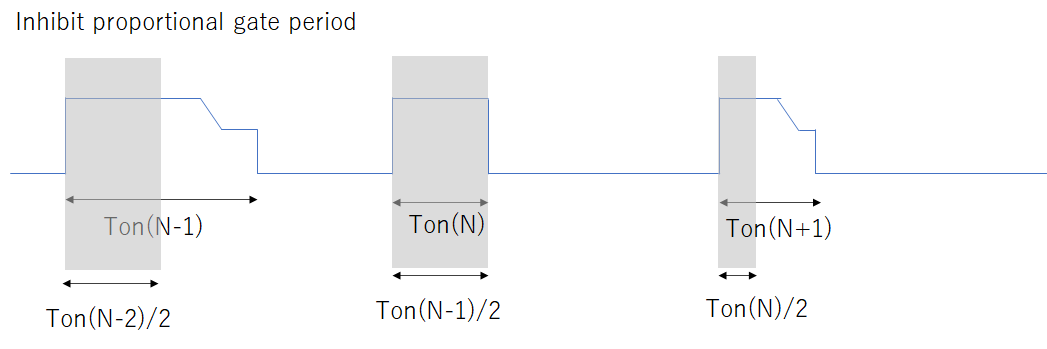

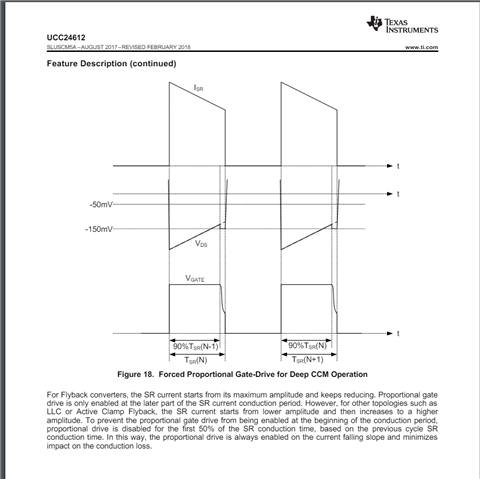

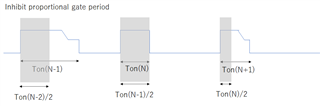

1.I have illustrated the transition of the proportional gate drive inhibition period. Is this understanding correct?

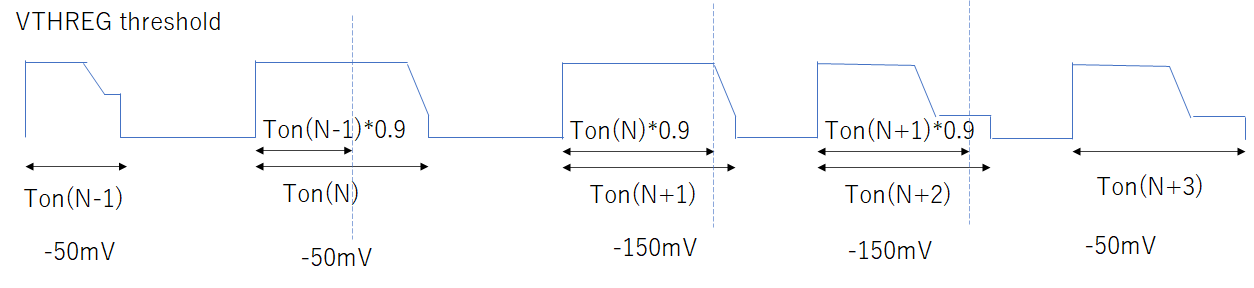

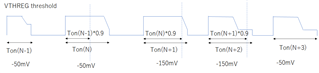

2,I have illustrated the timing of changes in the VTHREG threshold. Is this understanding correct?

Although the waveforms differ from the actual operating waveforms, I would like to confirm this as IC operation.