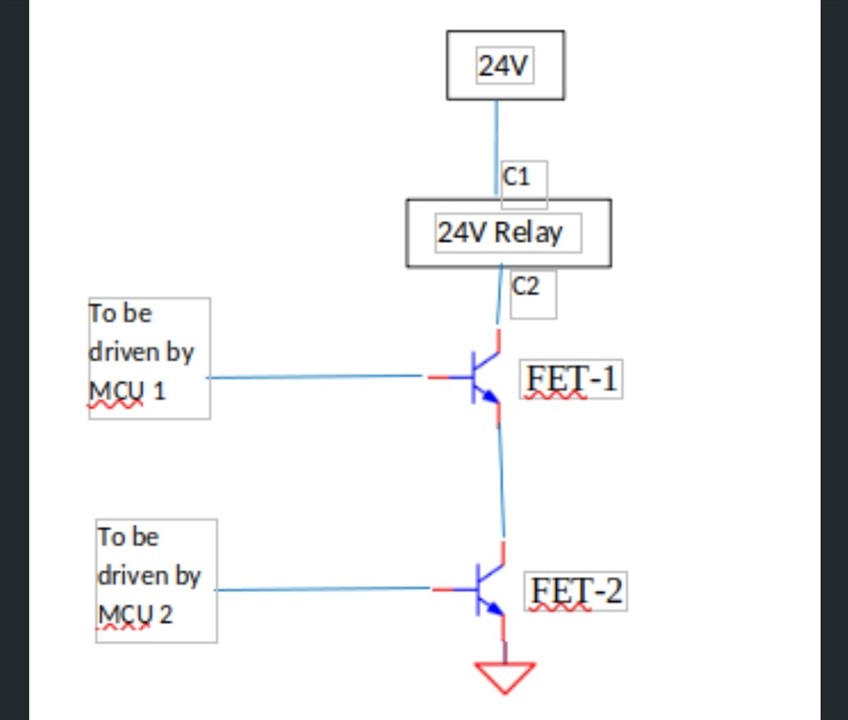

Please suggest the mosfet configuration for below requirement -

24V Relay details -

1. Rated voltage (Vdc)- 24V

2. COIL resistance – 350 ohm

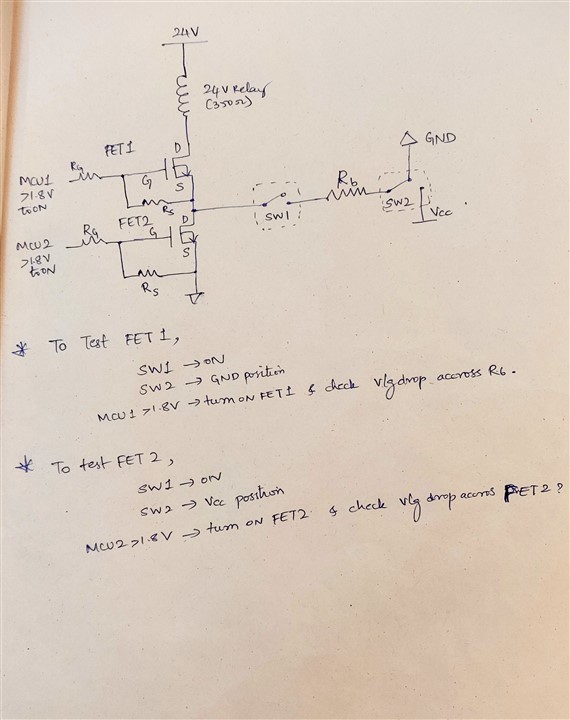

Both the FET's must be independently driven by 2 different MCU's. When both the FET's are switched ON, the 24V relay should be energized.

Please suggest FET's and connection configuration.

When power is cut off both the FET's shall be switched off.

Also provide procedure for self-check test of each FET's