Tool/software: Code Composer Studio

I am trying to program an MSP430FR2000 using CCS Version: 9.1.0.00010. I'm building a simple program I downloaded from the forum to get started. I'm getting the following error:

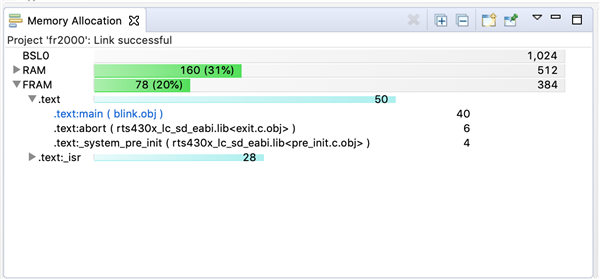

error #10099-D: program will not fit into available memory. placement with alignment fails for section "ALL_FRAM" size 0x1f0 . Available memory ranges:

FRAM size: 0x180 unused: 0x180 max hole: 0x180

Below is the code:

#include <msp430.h>

#include <stdint.h>

// #defines for simple communication protocol

#define READ 0

#define WRITE 1

// Global variables

uint8_t command, data, byteCount;

// Function prototypes

void UART_sendByte(uint8_t txByte);

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

byteCount = 0; // Initialize byteCount

// Configure Comparator input & output

P1DIR = 0xFF;

P1OUT = 0x00;

P2DIR = 0xFF;

P2OUT = 0x00;

PADIR = 0xFF;

PAOUT = 0x00;

P1SEL0 = BIT1 | BIT2 | BIT3; // Select eCOMP input function on P1.1/C1, UCA0 RXD and TXD

P1SEL1 = BIT1;

P2DIR = BIT0;

P2SEL1 = BIT0 | BIT6 | BIT7; // Select CPOUT function on P2.0/COUT, P2.6~P2.7: crystal pins

PM5CTL0 &= ~LOCKLPM5; // Disable the GPIO power-on default high-impedance mode

// to activate previously configured port settings

// Initialize crystal

//do

//{

// CSCTL7 = 0; // Clear XT1 fault flag

// SFRIFG1 = 0; // Clear fault flag

//} while (SFRIFG1 & OFIFG); // Test oscillator fault flag

//CSCTL4 = SELA__XT1CLK; // Set ACLK = XT1CLK = 32768Hz

// Configure UART

// From user's Guide Table of Baud Rates, 9600 baud at BRCLK = 32768

// UCOS16 = 0

// UCBRx = 3

// UCBRFx = 0

// UCBRSx = 0x92

UCA0CTLW0 = UCSWRST | UCSSEL__ACLK;

UCA0BRW = 3;

UCA0MCTLW = 0x9200;

UCA0CTLW0 &= ~UCSWRST; // Initialize eUSCI

UCA0IE = UCRXIE; // Enable USCI_A0 RX interrupt

// Setup eCOMP

CPCTL0 = CPPSEL0; // Select C1 as input for V+ terminal

CPCTL0 |= CPNSEL1 | CPNSEL2; // Select DAC as input for V- terminal

CPCTL0 |= CPPEN | CPNEN; // Enable eCOMP input

CPDACCTL = CPDACEN; // eCOMP output is selected as the buffer control source

CPDACDATA = 0x1030; // CPDACBUF1=VCC *3/4 CPDACBUF2=VCC *1/4

CPCTL1 |= CPEN | CPMSEL; // Turn on eCOMP, in low power mode

while(1)

{

__bis_SR_register(LPM3_bits | GIE); // Go to LPM3 with interrupts

__no_operation();

// Process received byte

// Note that byteCount is always incremented by 2. This allows

// __even_in_range usage for space-saving compiler optimization.

// See SLAU132 for more info.

switch(__even_in_range(byteCount,6))

{

case 2: // 1st byte received

command = data; // 1st byte is always command byte

if(command == READ) // Read Command

{ // Send response.

UART_sendByte(CPDACDATA_H); // Send the current DAC value

UART_sendByte(CPDACDATA_L);

byteCount = 0; // No further bytes to receive for READ

}

break;

case 4: // 2nd byte received

if(command == WRITE)

CPDACDATA_H = data;

break;

case 6: // 3rd byte received

if(command == WRITE)

CPDACDATA_L = data;

if(byteCount >= 6) // Check if all bytes received

byteCount = 0; // WRITE TIME command complete

break;

default: break;

}

}

}

// Function for sending UART byte via polling method

void UART_sendByte(uint8_t txByte)

{

while(!(UCA0IFG & UCTXIFG)); // Check if ready to TX

UCA0TXBUF = txByte; // Send the data byte

}

// UART interrupt service routine

#pragma vector=USCI_A0_VECTOR

__interrupt void USCI_A0_ISR(void)

{

data = UCA0RXBUF; // Read the byte

// Note that byteCount is always incremented by 2. This allows

// __even_in_range usage in main() for space-saving compiler optimization.

// See SLAU132 for info.

byteCount+=2; // Increment byte

__bic_SR_register_on_exit(LPM3_bits); // Wake from LPM

}

Below is the complete output from the build

**** Build of configuration Debug for project test ****

"C:\\ti\\ccs910\\ccs\\utils\\bin\\gmake" -k -j 8 all -O

Building file: "../main.c"

Invoking: MSP430 Compiler

"C:/ti/ccs910/ccs/tools/compiler/ti-cgt-msp430_19.6.0.STS/bin/cl430" -vmspx --use_hw_mpy=none --include_path="C:/ti/ccs910/ccs/ccs_base/msp430/include" --include_path="C:/Users/ryan.rogel/Documents/CCS/workspace/test" --include_path="C:/ti/ccs910/ccs/tools/compiler/ti-cgt-msp430_19.6.0.STS/include" --advice:power=all --advice:hw_config=all --define=__MSP430FR2000__ -g --printf_support=minimal --diag_warning=225 --diag_wrap=off --display_error_number --silicon_errata=CPU21 --silicon_errata=CPU22 --silicon_errata=CPU40 --preproc_with_compile --preproc_dependency="main.d_raw" "../main.c"

"../main.c", line 148: remark #1528-D: (ULP 3.1) Detected flag polling using UCA0IFG. Recommend using an interrupt combined with enter LPMx and ISR

Finished building: "../main.c"

Building target: "test.out"

Invoking: MSP430 Linker

"C:/ti/ccs910/ccs/tools/compiler/ti-cgt-msp430_19.6.0.STS/bin/cl430" -vmspx --use_hw_mpy=none --advice:power=all --advice:hw_config=all --define=__MSP430FR2000__ -g --printf_support=minimal --diag_warning=225 --diag_wrap=off --display_error_number --silicon_errata=CPU21 --silicon_errata=CPU22 --silicon_errata=CPU40 -z -m"test.map" --heap_size=160 --stack_size=160 --cinit_hold_wdt=on -i"C:/ti/ccs910/ccs/ccs_base/msp430/include" -i"C:/ti/ccs910/ccs/tools/compiler/ti-cgt-msp430_19.6.0.STS/lib" -i"C:/ti/ccs910/ccs/tools/compiler/ti-cgt-msp430_19.6.0.STS/include" --reread_libs --diag_wrap=off --display_error_number --warn_sections --xml_link_info="test_linkInfo.xml" --use_hw_mpy=none --rom_model -o "test.out" "./main.obj" "../lnk_msp430fr2000.cmd" -llibc.a

<Linking>

"../lnk_msp430fr2000.cmd", line 132: error #10099-D: program will not fit into available memory. placement with alignment fails for section "ALL_FRAM" size 0x1f0 . Available memory ranges:

FRAM size: 0x180 unused: 0x180 max hole: 0x180

error #10010: errors encountered during linking; "test.out" not built

>> Compilation failure

makefile:141: recipe for target 'test.out' failed

gmake[1]: *** [test.out] Error 1

makefile:137: recipe for target 'all' failed

gmake: *** [all] Error 2

**** Build Finished ****