Other Parts Discussed in Thread: LM2903, INA381-Q1, INA225-Q1, INA225, TPS2H000-Q1

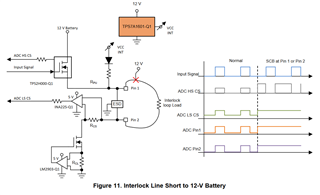

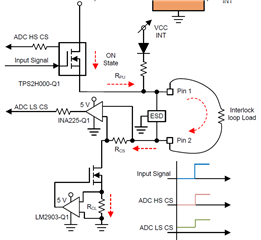

Why is a comparator, in a Schmidt trigger configuration, used for the low side current limit in the tida-01445 design?

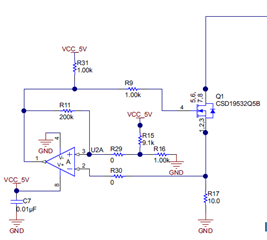

From my understanding the LM2903 comparator is used to limit the dynamic state current as well as the short to battery fault current to 50 mA (49.3 mA - 51.5 mA with hysteresis). Will the output of the comparator not switch back and forth rapidly between 0 and 5V? The FET is probaly not fast enough to completely switch on and off, in combination with C4, smoothing the interlock current.

Still, I guess, the output of the LM2903 will resonate in the MHz range? Why was this the preferred solution, compared to an opamp, that regulates the current via the FET with an analog voltage level? I can imagine the resonating output to become an EMI issue. Therefore, I am interested why this design approach was chosen. Maybe there are some considerations, I don't see at the moment.

Thank for the clarification.

Best regards