Other Parts Discussed in Thread: LM5026

Hello, Texas team.

I have built up a PMP22075 using the gerbers etc supplied.

The design is described as having an input voltage range of 9V to 60V.

My Problem - But when I reduce the input voltage, the output starts to drop from nominally 12V once the input voltage is less than approximately 10.75V.

Investigation so far - Duty Cycle - As expected, I can see the duty cycle of OUT_A of the LM5026 increase as the input voltage reduces.

BUT the duty cycle hits a limit of about 73% - when the input voltage equals 10.75V approx.

- With DCL connected directly to RT on the LM5026, we should be programming the maximum duty cycle.

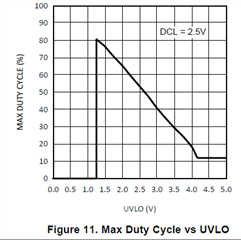

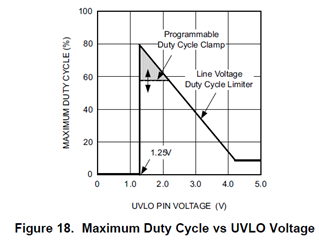

- There is also a relationship with duty cycle and the UVLO voltage - Shown in Figure 11 and Figure 18 of the LM5026 data sheet.

- The UVLO voltage is set by the resistor divider comprising R10, R13 and R17.

- This appears to give 1.45V when Vin = 9V (9V x 10.5 / (10.5 + 53.6 + 1))

- If UVLO is 1.45V then We'd expect max duty cycle to be less than 80% ?? - as shown in Figures 11 and 18.

My question: Please advise how I can achieve a full 12V output when the input voltage is at the low end of the range (from 9V to 10.5V say)?

(Our application requires a minimum input voltage of 10.5V).

Thanks in advance.