Tool/software: WEBENCH® Design Tools

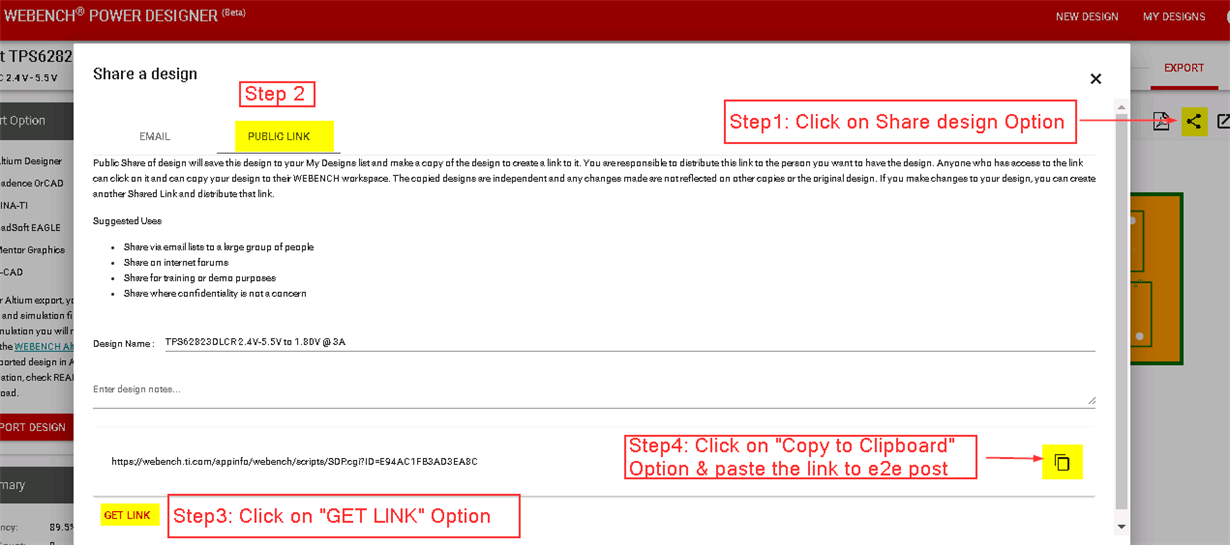

I'm seeing some odd behaviour in WEBENCH when I 'create a custom part' for Cout. This can be illustrated by comparison with Amod's shared design https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=2E2237E366C1AD75, which uses for Cout a 47μF ceramic, quantity 2 (derated to 39μF total with voltage bias) with ESR of 2.082mΩ each

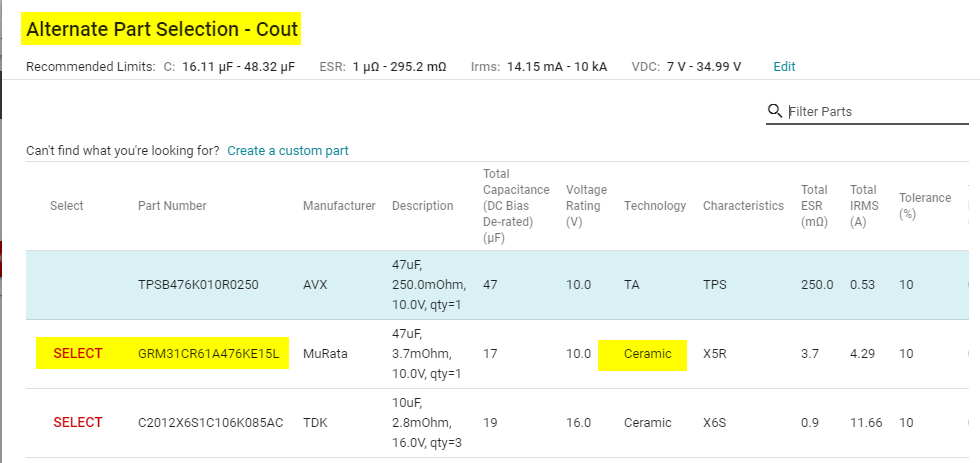

I wanted to try some slightly different capacitors, so I started by creating a new shared design webench.ti.com/.../SDP.cgi using exactly the same components except for Cout I created a custom capacitor of 39µF with ESR of 1.041mΩ:

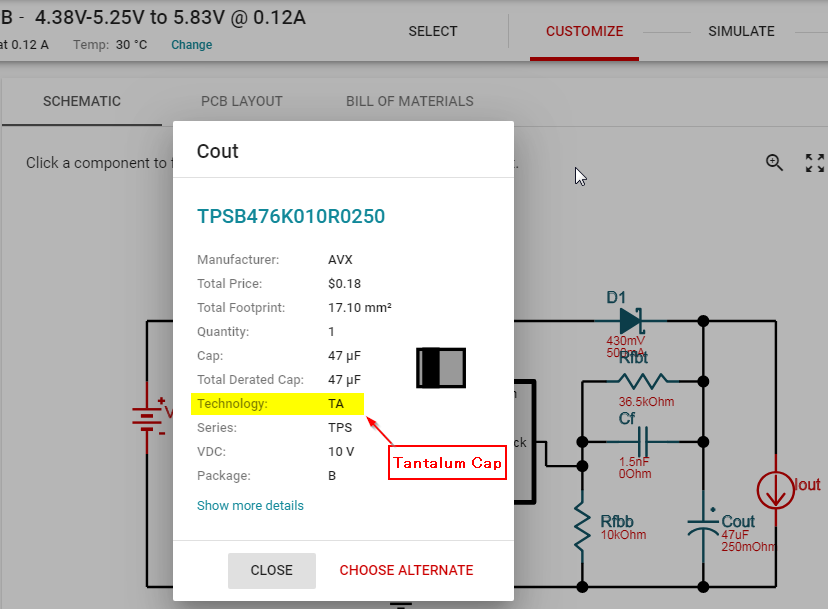

The first problem is that interrogating "More details" for this part shows an ESR of 250mΩ, unchanged from the default capacitor WEBENCH currently suggests for this design:

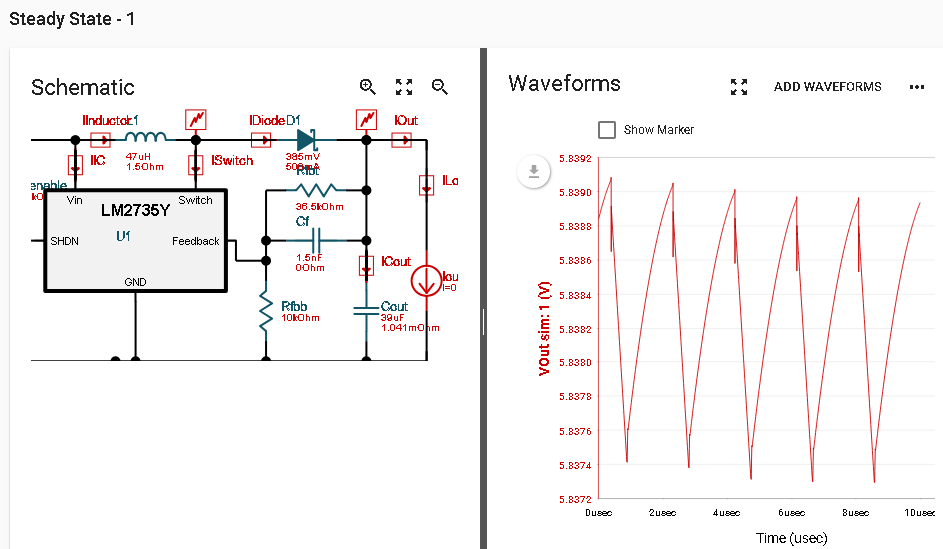

The next issue is with the simulation. The capacitor looks correct in the schematic shown on the simulation page:

However, the steady-state simulation result shows huge spikes on Vout:

The Vout waveform does not appear to be consistent with the current through Cout:

If the ESR was 1.041mΩ as intended, the spikes on Vout should be about 0.4mV peak-to-peak when the regulator switch turns on and about 0.2mV p-p when the switch turns off, or if the ESR is wrongly using the 250mΩ value the spikes should be about 100mV p-p and about 50mV p-p respectively, whereas in fact they are about 1.1V p-p and 40mV p-p respectively. Also, the other features of the current waveform (roughly rectangular, with droop in the high state) do not show up on Vout, either scaled by ESR or integrated by the capacitance (examples of each are in my previous post "Suggested output capacitor gives excessive output ripple" (https://e2e.ti.com/support/tools/sim-hw-system-design/f/234/t/784345).

Note that the above issues are different from the bug with parallel capacitors ("Qty" greater than 1) already reported as point 2(d) in the thread "Inconsistent options for alternate parts" (https://e2e.ti.com/support/tools/sim-hw-system-design/f/234/t/779121). In that case "More details" displays the wrong ESR (multiplied by Qty rather than divided) but the simulation appears to be correct. In the above case the ESR is displayed as that of the default component and the simulation looks completely wrong, unless I'm missing something.